## 6.2 多孔铜的制备

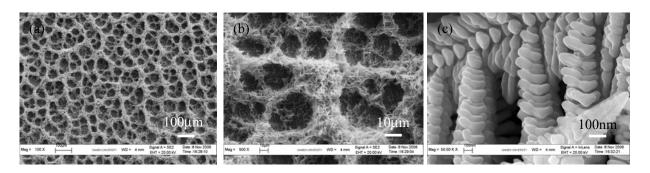

为了制备适合于合金电极集流体的多孔铜,我们采用不同电镀工艺。首先在未含添加剂聚乙二醇和 NaCl 的电镀液中制备得到多孔铜(电镀工艺如表 2-3),其表面形貌示于图 6.1。可观察到多孔铜的孔洞分布不均匀,孔壁很薄,且不均匀;再由局部放大图

图 6.1 未含添加剂聚乙二醇和 NaCl 的电镀液中制备所得多孔铜的 SEM 图

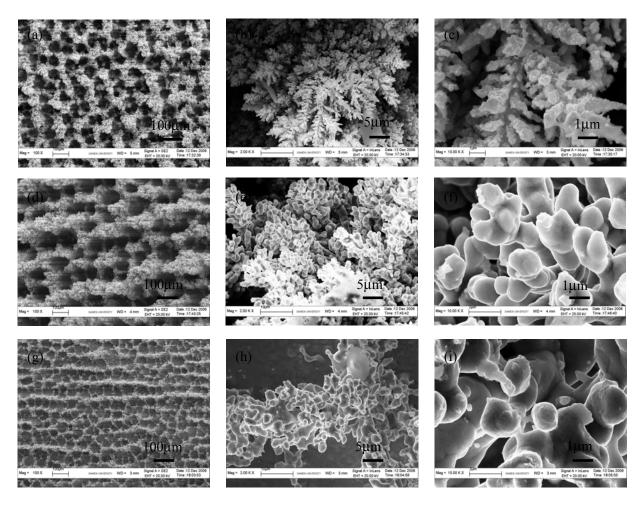

图 6.2 未含添加剂聚乙二醇和 NaCl 的电镀液制得多孔铜, 经 600  $\mathbb{C}$  (a, b, c)、700  $\mathbb{C}$  (d, e, f) 和 800  $\mathbb{C}$  (g, h, i) 条件下热处理 1 小时后的 SEM 图

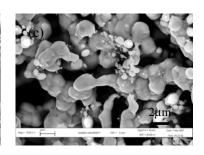

可看出多孔铜主要由叶状枝晶组成,结构疏松,与基底结合力较差,极易与基底剥离。 为了改善多孔铜与基底间的结合力,我们将其经 600 ℃、700 ℃和 800℃条件下热处理 1 小时,表面形貌分别示于图 6.2。由图可观察到随着热处理温度的升高,多孔铜的多孔 结构逐渐遭到破坏,再由局部放大图可看出多孔铜的枝晶随着温度的升高而逐渐消失, 但即使在 800 ℃下热处理 1 小时后的多孔铜表面也不平整,且与基底间结合力仍然不 够理想,这可能是由于未加入添加剂时所制得的多孔铜枝晶过多所致。

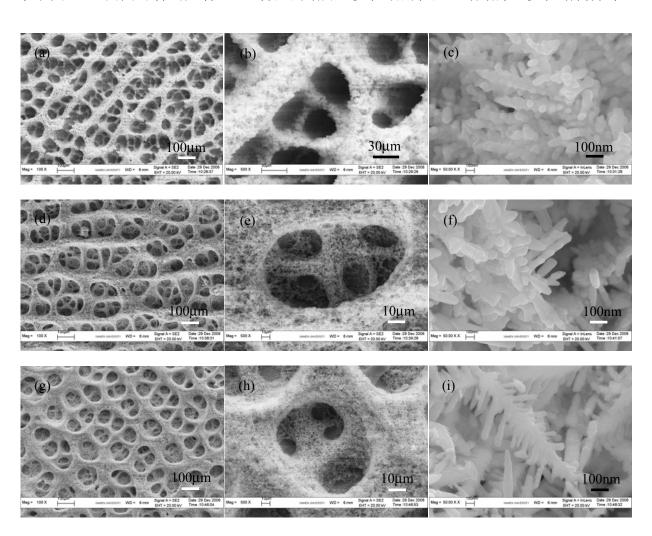

为了改善多孔铜的多孔结构,使其孔道分布更均匀,孔壁更厚,枝晶更少,我们在上述电镀液中添加 20 mg/L 的聚乙二醇,和 0.1~0.5 mM NaCl,所制得多孔铜表面形貌示于图 6.3。由图可看出随着 NaCl 含量的增加,多孔铜的孔壁逐渐增厚,多孔结构分布

图 6.3 含添加剂聚乙二醇 20.0 mg/L, NaCl 含量分别为 1 mM(a, b, c)、10 mM(d, e, f)和 50 mM(g, h, i)的电镀液电镀制备所得多孔铜的 SEM 图

更加均匀。再由局部放大图可清晰观察到,添加 NaCl 和聚乙二醇后,枝晶明显减少,与基底间结合力较未加入添加剂前好。其中含 20.0 mg/L 聚乙二醇,50 mM NaCl 的电镀液制备所得多孔铜的性能最佳。

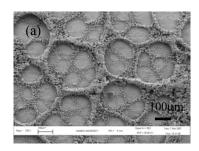

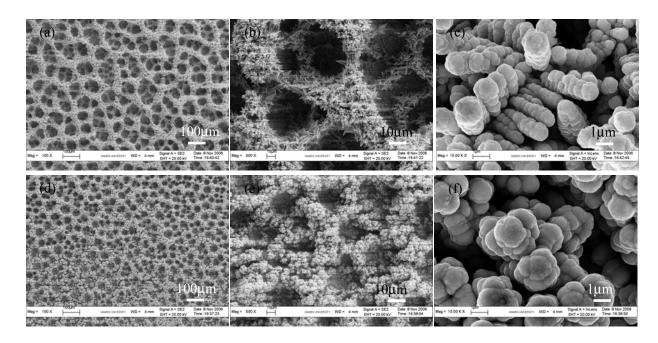

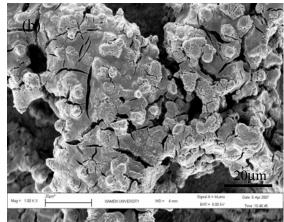

为了进一步增强多孔铜与基底间的结合力,我们将含添加剂 20.0 mg/L 聚乙二醇,50 mM NaCl 的镀液制备所得多孔铜经 800 ℃热处理 1 小时,表面形貌如图 6.4 所示。由图可观察到其多孔结构遭到严重破坏,特别是镀层厚度变薄,孔壁变窄,这是由于新鲜制备的多孔铜结构疏松,经 800 ℃热处理后结构变结实,以及在 800 ℃高温条件下多孔铜会部分升华所致。但经热处理后多孔铜表面比较平整,与基底间的结合力也变好,适合于锂离子电池的集流体;同时我们还可观察到孔壁上仍然存在大量的无规则的多孔结构,可缓解合金材料在嵌锂过程中的体积膨胀,达到改善合金电极电化学性能的目的。

图 6.4 含 20.0 mg/L 聚乙二醇(PEG), 50 mM NaCl 的镀液电镀制得多孔铜, 经 800 ℃热处理 1 小时后的 SEM 图

# 6.3 未经热处理的多孔铜上电镀锡铜合金的性能研究

为了改善多孔铜与基底间的结合力,我们最初采用在多孔铜上直接电镀合金来稳定骨架结构,同时作为活性材料。图 6.5 给出未含添加剂聚乙二醇和 NaCl 的镀液电镀制得多孔铜上电镀 5 分钟(a, b, c)和电镀 30 分钟(d, e, f) 锡铜合金后的 SEM 图。由图可观察到,锡铜合金是沿着多孔铜的枝晶生长,自身形状为球形。但即使电镀 30 分钟后,电极仍然呈枝晶状,电极与基底间的结合力未能得到较大的改善,所以该方法难以达到改善多孔铜与基底间的结合力的目的。

图 6.5 未含添加剂聚乙二醇和 NaCl 的镀液电镀制得多孔铜上电镀 5 分钟(a, b, c)和电镀 30 分钟(d, e, f) 锡铜合金后的 SEM 图。

同时我们以含添加剂 20.0 mg/L 聚乙二醇(PEG), 50 mM NaCl 的镀液电镀制得的多 孔铜为基底电镀锡铜合金,其表面形貌示于图 6.6。由图可看出,锡铜合金仍然是沿着 多孔铜基底形貌生长的,自身形状为球形,但由于加入添加剂后的镀液电镀制备所得多 孔铜枝晶较少,所以表面更加平整,其与基底间的结合力比未含添加剂的镀液制得的多 孔铜上电镀锡铜合金更好。

图 6.6 含添加剂 20.0 mg/L PEG, 50 mM NaCl 的镀液中制得的多孔铜电镀锡铜合金后的 SEM 图

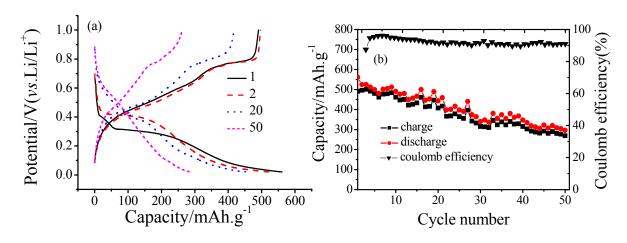

图 6.7 为上述样品的充放电曲线和循环性能曲线。由锡铜合金的放电曲线可观察到前 20 周循环中放电曲线均在 0.4 V 和 0.1 V 附近分别出现了电位平台,这是  $Cu_6Sn_5$  合金

的特征放电平台<sup>[8-12]</sup>,20周循环后该电位平台大幅度正移,且长度变短。由其循环性能曲线可看出该结构的锡铜合金电极的比容量随着循环次数增加迅速减小,这主要是归因于合金材料与基底间的结合力不好,充放电过程中发生脱落所致。

图 6.7 含添加剂 20.0 mg/L PEG, 50 mM NaCl 的镀液中制得的多孔铜电镀锡铜合金后的充放电曲线(a)和循环性能曲线(b)

## 6.4 热处理后多孔铜上电镀锡铜合金的性能研究

### 6.4.1 表面形貌和结构分析

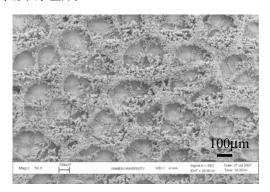

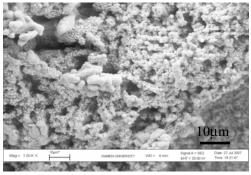

图 6.8 给出含添加剂 20.0 mg/L 聚乙二醇, 50 mM NaCl 的镀液中制得的多孔铜经热处理 1 小时后电镀锡铜合金后的 SEM 图。可观察到锡铜合金仍然是沿着多孔铜本身的形貌生长,电镀过后在孔壁上仍然存在大量的无规则孔洞,这有利于缓解锡铜合金在嵌锂过程中的体积膨胀。图 6.9 给出相应的 XRD 图。由图可知镀层主要由 Cu<sub>6</sub>Sn<sub>5</sub> 合金和少量单质锡组成。

图 6.8 热处理后多孔铜上电镀锡铜合金后的 SEM 图

图 6.9 热处理后多孔铜上电镀锡铜合金后的 XRD 图

## 6.4.2 充放电性能表征

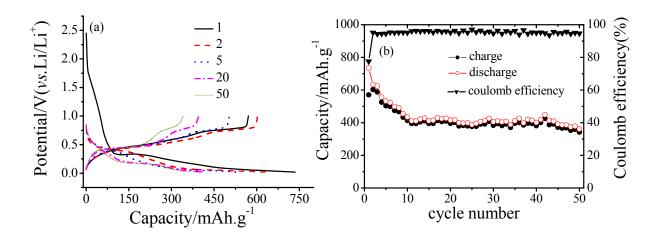

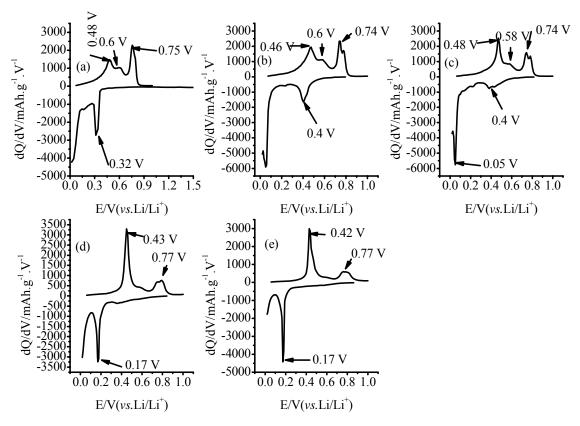

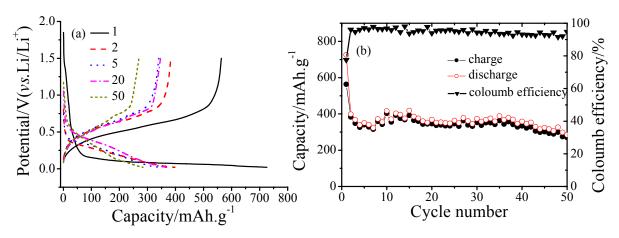

图 6.10 和图 6.11 分别为热处理后多孔铜上锡铜合金的充放电曲线、循环性能曲线 和相应的微分容量曲线。由充放电曲线(图 6.10 a)和其相应微分容量曲线(图 6.11) 可观察到,首次放电过程中在 0.32 V 以上(合金嵌锂之前)产生了大约 75 mAh/g 的不 可逆容量,这是由于该合金电极表面积大,电解液的还原分解严重所致。由首次放电曲 线和其相应微分容量曲线还可观察到,首次放电过程在 0.32 V 和接近 0.0 V 附近分别给 出电位平台。其中 0.32 V 附近的电位平台从第 2 周循环开始正移至 0.4 V 附近,在随后 的循环中无明显变化,表征 Cu<sub>6</sub>Sn<sub>5</sub> 合金相转变为 Li<sub>2</sub>CuSn 合金相过程。当电极经过 20 周循环后这一电位平台明显变短,且在 0.17 V 附近出现了一个新的电位平台。由充放电 曲线还可以观察到20周循环后在电位大于0.4 V处出现了放电容量。当电极循环50周 后,在 0.2 V 以上基本变为一条斜线,然后在 0.17 V 附近的电位平台变长。由图 6.10 a 和图 6.11 还可观察到锡铜合金的充电(脱锂)曲线的平台电位无明显变化,但当电极循 环 20 周后, 0.75 V 附近的电位平台变短, 随着循环次数增加进一步变短, 这与放电曲 线相对应。锡铜合金的充放电循环性能曲线由图 6.10 b 给出。由图可得出锡铜合金首次 放电容量为 735 mAh/g, 首次充电容量为 571 mAh/g; 第 2 周至第 10 周循环容量迅速下 降, 充电容量下降到 434 mAh/g; 经过 10 周循环后容量降低速度明显减缓, 经过 50 周 循环后容量保持在342 mAh/g。图6.10 b 给出首次库伦效率为78%,随着循环次数的增

加迅速增加至95%左右,最后趋于基本稳定。

图 6.10 热处理后多孔铜上锡铜合金的充放电曲线(a)和循环性能曲线(b)

图 6.11 热处理后多孔铜上锡铜合金充放电 1 周(a)、2 周(b)、5 周(c)、20 周(d)和 50 周(e)循环的微分容量曲线

## 6.4.3 CV 表征

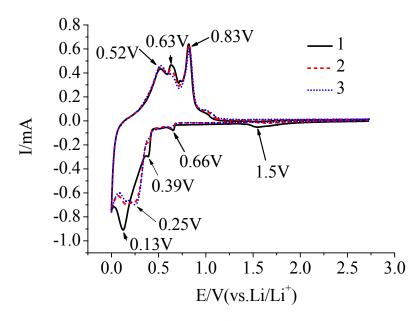

热处理后多孔铜上锡铜合金的 CV 曲线如图 6.12 所示,可观察到在首次循环过程中,于 1.5 V 附近给出一个不可逆还原峰,此峰在随后的循环中几乎完全消失,对应 SEI 膜的生成,并说明 SEI 膜具有较好的稳定性,是该结构的锡铜合金电极循环性能较好的一个重要原因。在首次循环中还在 0.66 V、0.39 V 和 0.13 V 附近处分别给出电流峰。其中 0.66 V 和 0.39 V 处的电流峰可能是少量单质锡的嵌锂峰,0.13 V 处的电流峰为 Cu<sub>6</sub>Sn<sub>5</sub>合金的特征嵌锂峰。我们同时还观察到 0.66 V 和 0.39 V 附近的电流峰随着循环周数增加而逐渐消失,0.13 V 处的电流峰逐渐正移,循环 3 周后正移至 0.25 V,这与充放电曲线中电位平台正移相对应。首次脱锂过程中,锡铜合金在 0.52 V、0.63 V 和 0.83 V 附近给出电流峰,其中 0.52 V 和 0.83 V 处的电流峰随着循环周数增加无明显变化,但 0.63 V 处的电流峰却逐渐消失。

图 6.12 热处理后多孔铜上锡铜合金的 CV 图

## 6.4.4 热处理后多孔铜上锡铜合金的 EIS 研究

### 6.4.4.1 热处理后多孔铜上锡铜合金在不同温度下阻抗谱基本特征

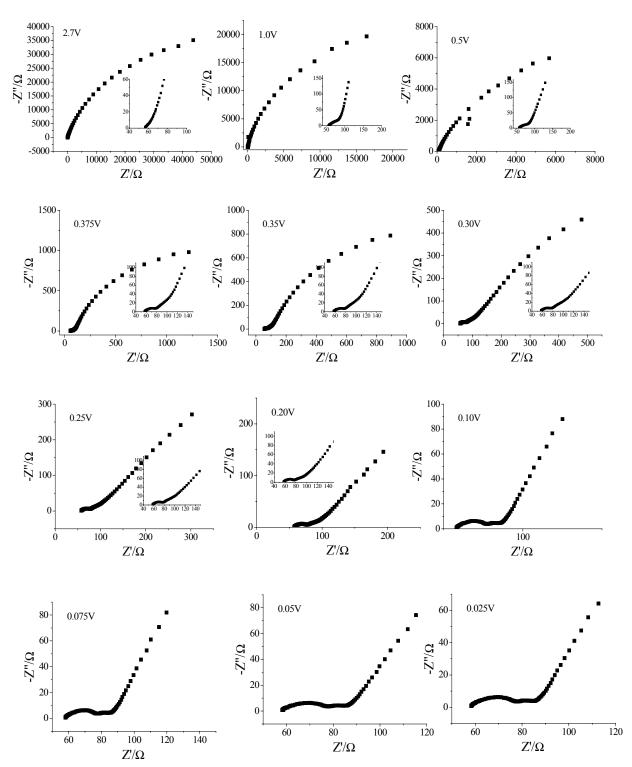

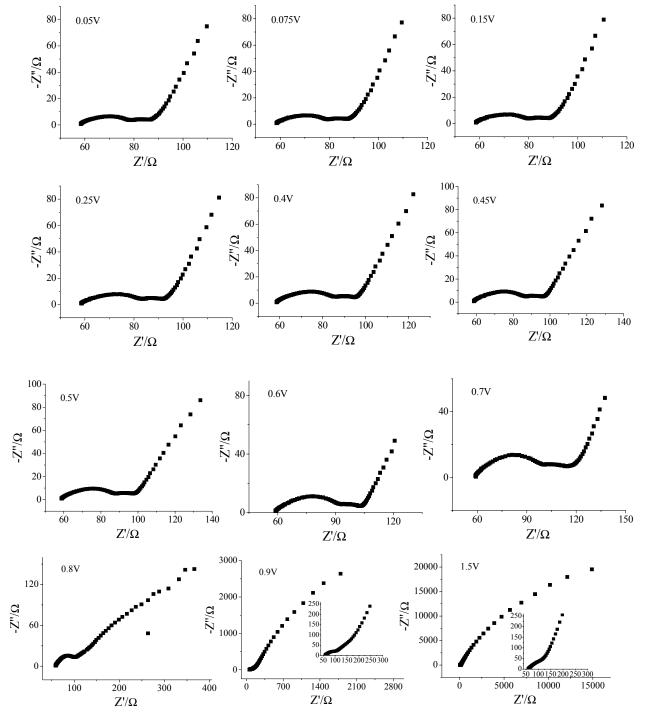

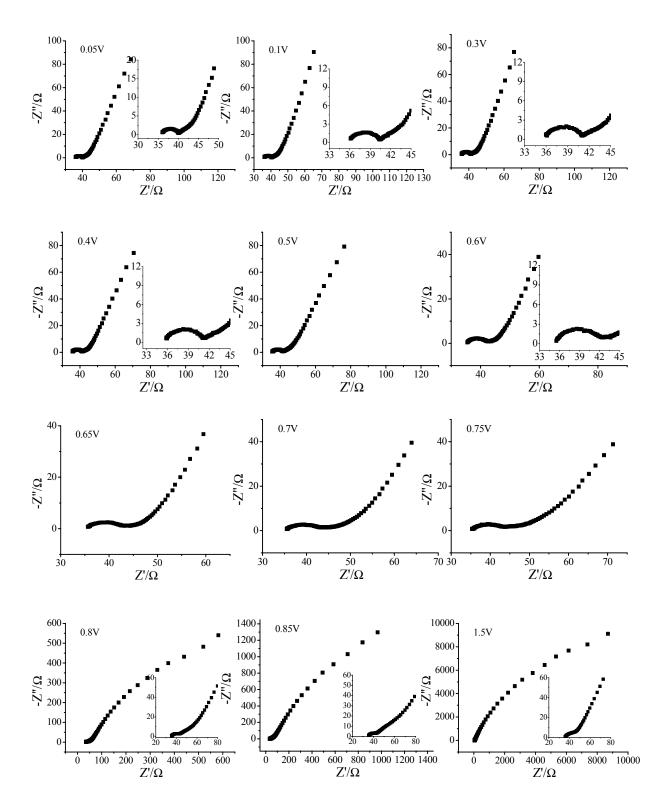

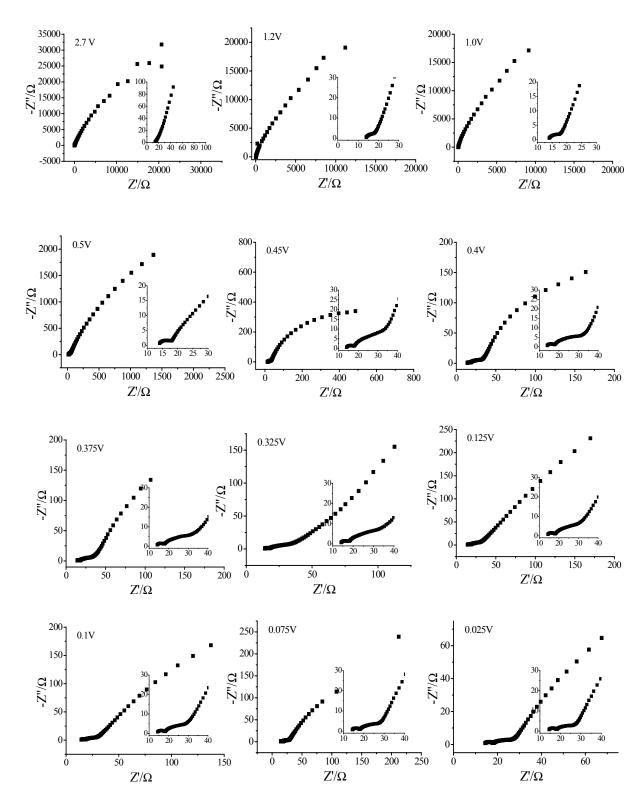

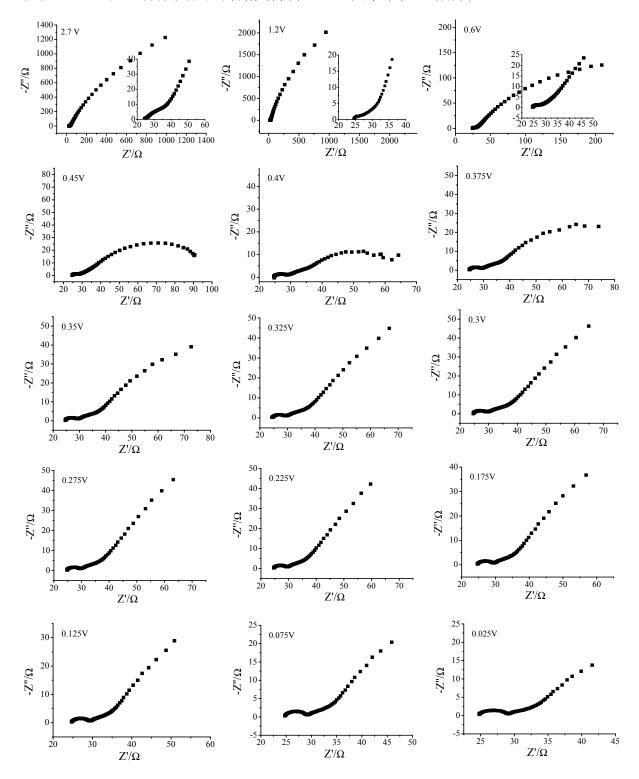

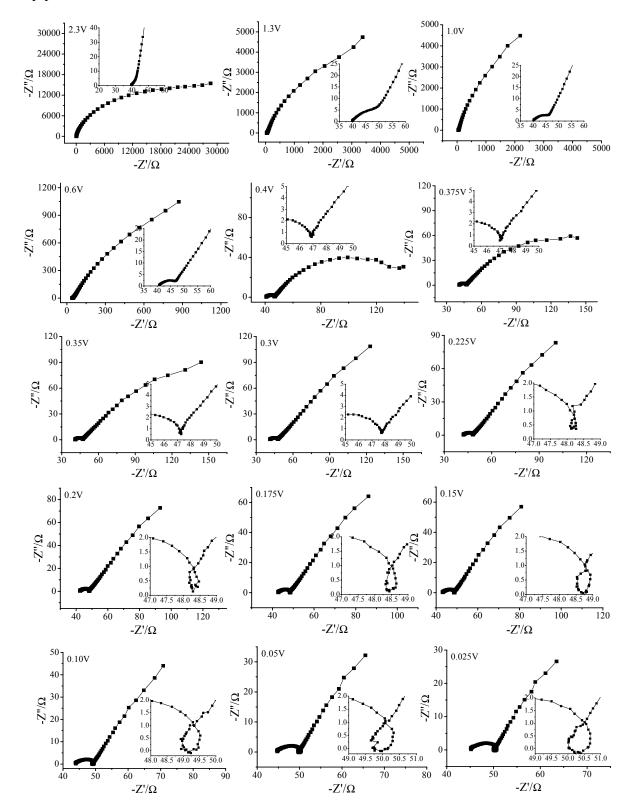

图 6.13 和图 6.14 给出热处理后多孔铜上锡铜合金在 0℃条件下首次嵌/脱锂过程的 阻抗谱。由首次嵌锂过程的阻抗谱(图 6.13)可观察到,锡铜合金在开路电位 2.7 V时 的 Nyquist 图由一个曲率半径很大的圆弧组成,表现为阻塞电极特征,即无锂离子的嵌 入/脱出。当电极电位极化到 1.0 V 时,Nyquist 图中的高频区域给出一段圆弧,表明 SEI 膜的生成。当电极电位进一步降低至 0.5 V 后,中低频圆弧曲率半径开始减小。当电极 电位降低到 0.375 V 时, Nyquist 图转变为 3 部分组成,即高频圆弧、中频圆弧和低频曲 率半径很大的圆弧。由第四章分析结果可知,高频圆弧代表锂离子穿过电极表面 SEI 膜 的阻抗<sup>[13-18]</sup>,中频圆弧代表电荷传递阻抗,低频圆弧代表相变阻抗<sup>[19-22]</sup>。当电极电位进 一步降低时,高频和中频圆弧变化不大,低频圆弧逐渐转变为一条斜线,至 0.25 V 时完 全转变为一条斜线,表明由 Cu<sub>6</sub>Sn<sub>5</sub> 相转变为 Li<sub>2</sub>CuSn 相的相变过程结束。当电极电位降 低到 0.1 V 后,中频圆弧完全分离出来,同时低频斜线开始弯曲,说明新相变的出现, 即 Li<sub>2</sub>CuSn 转变为 Li<sub>4</sub>4Sn 相,对应于充放电曲线中的接近 0.0 V 附近的电位平台: 当电 极电位进一步降低直至嵌锂完毕(0.025V)时, Nyquist 图均无明显变化。在脱锂过程 中(图 6.14), 当电极电位低于 0.45 V 时, Nyquist 图均由高频圆弧、中频圆弧和低频斜 线组成; 当电极电位升高到 0.45 V 后, 高频和中频圆弧无明显变化, 但低频斜线转变为 一段圆弧,指示相变阻抗的出现,这与充放电曲线中 0.48 V 附近出现充电平台相一致; 当电位升高到 0.6 V 时,低频圆弧转变为一条斜线,直到 0.8 V 时再次转变为一段圆弧, 代表新的相变产生,这与充放电曲线中在 0.76 V 附近出现充电平台相一致; 当电极电位 升高到 1.5 V 后,由于 Cu<sub>6</sub>Sn<sub>5</sub> 合金电极的脱锂过程完毕,因此 Nyquist 图转变为由高频 圆弧和中低频曲率半径很大的圆弧组成。

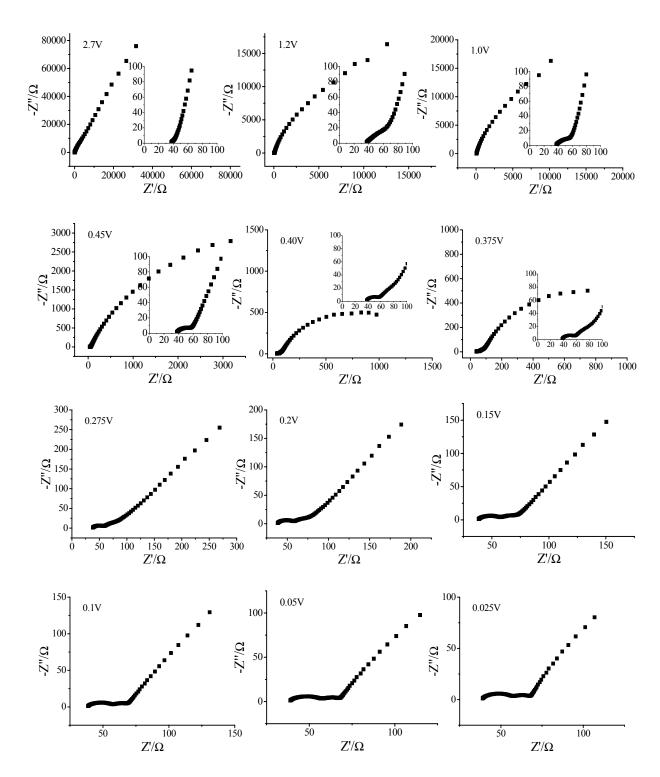

图 6.15 和图 6.16 给出热处理后多孔铜上锡铜合金在 10℃下首次嵌/脱锂过程的阻抗 谱。由图 6.15 可观察到,开路电位 2.7 V 时,Nyquist 图仍然由一段曲率半径很大的圆 弧构成; 当电极电位极化到 1.2 V 时,高频开始出现一段圆弧,代表 SEI 膜的生成; 随着电极电位的进一步降低,高频圆弧和中低频圆弧分离更加明显; 当电极电位极化到 0.4 V 时,Nyquist 图同样由 3 段圆弧组成,即高频圆弧、中频圆弧和低频圆弧,; 但高频、中频和低频圆弧的曲率半径均比 0℃时小,这表明温度增大,界面阻抗减小。随着电极

电位进一步降低,低频圆弧同样逐渐转变为斜线,当降低至 0.275 V 时完全转变为一条斜线。当电极电位进一步降低到 0.1 V 后,低频斜线又再次转变为一段圆弧,并且该圆弧比 0℃时更加明显,说明相变更加容易,更利于锂离子的嵌入。

由 10℃下脱锂过程的阻抗谱(图 6.16)可观察到,当电极电位小于 0.4 V 时,Nyquist 图均由高频圆弧、中频圆弧和低频斜线组成;当电极电位升高至 0.4 V 后,低频斜线转变为一段圆弧,说明相变的产生,这同样与充放电结果中在 0.45 V 附件出现电位平台相对应。当电极电位升高至 0.65 V 后,由于 0.45 V 附近的相变结束,低频圆弧转变为斜线;但当电极电位升高到 0.8 V 后,低频斜线再次转变为一段圆弧,其结果与 0℃条件下较为相似,但转变电位略有差别。当电极电位升高到 1.5 V 时,由于脱锂过程进行完毕,Nyquist 图则由高频圆弧和中低频曲率半径较大圆弧组成。

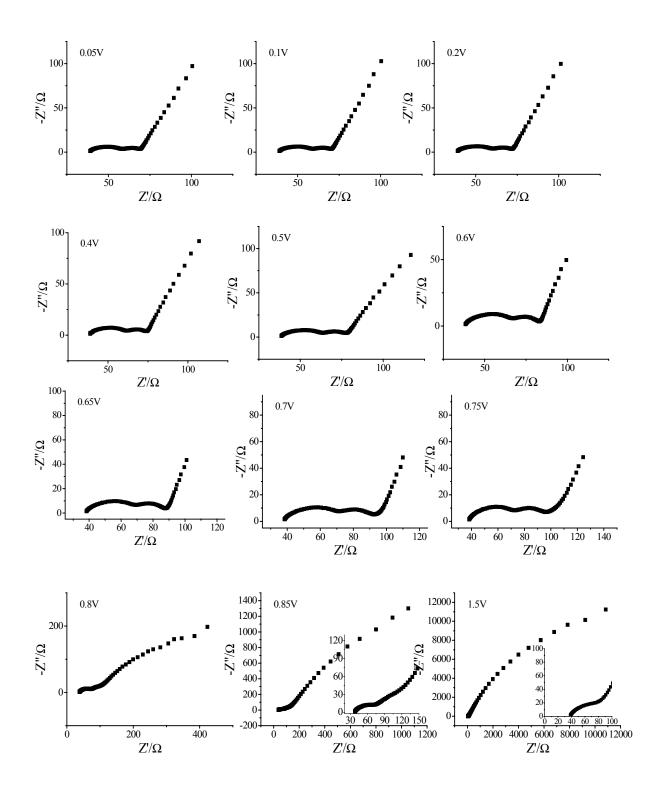

图 6.17 和图 6.18 分别给出热处理后多孔铜上锡铜合金在 25℃条件下,首次嵌/脱锂过程的阻抗谱。由首次嵌锂过程的阻抗谱(图 6.17)可观察到,开路电位 2.7 V时的 Nyquist 图仍然由一段曲率半径很大的圆弧组成。当电极电位负移至 1.2 V时,Nyquist 图中的高频区域出现了一段圆弧,且随着电极电位的进一步降低,高频圆弧和中低频圆弧分离更加明显。当电极电位降低至 0.45 V时,Nyquist 图转变为 3 段圆弧组成,即高频圆弧,中频圆弧和低频圆弧。其中高频圆弧代表锂离子穿过电极表面 SEI 膜的阻抗,中频圆弧代表电荷传递阻抗,低频圆弧代表晶体相变阻抗。当电极电位降低至 0.325 V时,低频圆弧同样转变为一条斜线;当电极电位进一步降低至 0.1 V后,此斜线再次转变为一段圆弧,直到嵌锂完毕,指示新相的产生。

脱锂过程中(图 6.18),阻抗特征与 0℃和 10℃条件下略有不同,当电极电位低于 0.8 V 时 25℃条件下锡铜合金电极的 Nyquist 图均由高频圆弧、中频圆弧和低频斜线组成,在 0.4 V 附件未给出低频圆弧; 当电极电位升高到 0.8 V 后低频斜线转变为一段圆弧。当电极电位升高到 1.5 V 后,由于脱锂过程完毕,所以 Nyquist 图由高频圆弧和中低频曲率半径很大的圆弧组成。

图 6.19 和图 6.20 给出热处理后多孔铜上锡铜合金在 40℃条件下,首次嵌/脱锂过程的阻抗谱。由其首次嵌锂过程的阻抗谱(图 6.19)可观察到,开路电位 2.7 V 时,Nyquist 图仍然由一段曲率半径很大的圆弧组成。当电极电位极化到 1.2 V 时,Nyquist 图中的高频给出一段新的圆弧,说明 SEI 膜的生成;且随着电位降低,高频和中低频圆弧分离更加明显。当电极电位降低到 0.5 V 时,Nyquist 图转变为 3 段圆弧组成,即高频圆弧、中

频圆弧和低频圆弧。与前面讨论一致,高频圆弧代表锂离子穿过电极表面 SEI 的阻抗,中频圆弧代表电荷传递阻抗,低频圆弧代表晶体相变阻抗。比较  $0^{\circ}$  、 $10^{\circ}$  、 $25^{\circ}$  个和  $40^{\circ}$  时各电极阻抗分离为 3 段圆弧的电位可知,随温度升高,其电位也增大,这是由于温度升高,界面阻抗减小,出现电荷传递和相变阻抗的电位提前(即电位正移)。由图 6.19

图 6.13 热处理后多孔铜上锡铜合金在 0℃下首次嵌锂过程的阻抗谱

观察到当电极电位降低到 0.45 V 时,Nyquist 图完全分离为 3 段圆弧。当电极电位下降 到 0.325 V 后,低频圆弧转变为一条斜线; 当电极电位降低到 0.125 V 时此斜线再次转 变为一段圆弧,直至嵌锂完毕。

脱锂过程与 25℃时情况较为相似, 当电极电位低于 0.8 V 时 Nyquist 图均由高频弧、中频圆弧和低频斜线组成; 电极电位升高至 0.8 V 后, 低频斜线则转变为一段圆弧; 当

图 6.14 热处理后多孔铜上锡铜合金在 0℃下首次脱锂过程的阻抗谱

电极电位升高到 1.5 V 后,由于脱锂过程完毕,所以 Nyquist 图由高频圆弧和中低频曲率半径很大的圆弧组成。

图 6.15 热处理后多孔铜上锡铜合金在 10℃下首次嵌锂过程的阻抗谱

图 6.16 热处理后多孔铜上锡铜合金在 10℃下首次脱锂过程的阻抗谱

图 6.17 热处理后多孔铜上锡铜合金在 25℃下首次嵌锂过程的阻抗谱

图 6.18 热处理后多孔铜上锡铜合金在 25℃下首次脱锂过程的阻抗谱

图 6.19 热处理后多孔铜上锡铜合金在 40℃下首次嵌锂过程的阻抗谱

图 6.20 热处理后多孔铜上锡铜合金在 40℃下首次脱锂过程的阻抗谱

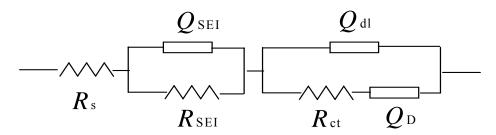

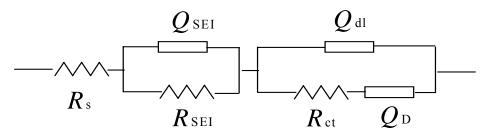

## 6.4.4.2 模拟电路的选取

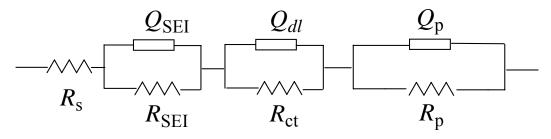

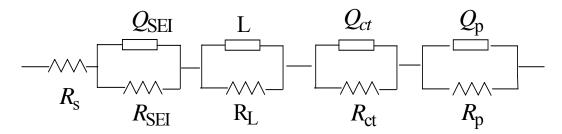

根据文献报道并结合实验结果我们提出了两种等效电路对实验数据进行模拟,如图 6.21和6.22。当阻抗谱为两段圆弧和一条斜线组成时采用等效电路1进行模拟,当阻抗谱 为3段圆弧组成时则采用等效电路2进行模拟。其中 $R_{\rm s}$ 代表欧姆电阻, $R_{\rm SEI}$ 、 $R_{\rm ct}$ 和 $R_{\rm p}$ 分别 为SEI膜电阻、电荷传递电阻和晶体相变电阻,SEI膜电容 $C_{\rm SEI}$ 、双电层电容 $C_{\rm dl}$ 、晶体相 变电容 $C_{\rm p}$ 以及扩散阻抗分别用恒相角元件(CPE) $Q_{\rm SEI}$ 、 $Q_{\rm dl}$ 、 $Q_{\rm p}$ 和 $Q_{\rm D}$ 表示。CPE的导纳 响应表达式如下:

$$Y = Y_0 \omega^n \cos\left(\frac{n\pi}{2}\right) + jY_0 \omega^n \sin\left(\frac{n\pi}{2}\right)$$

(6-1)

其中 $\omega$ 为角频率, j 为虚数单位 $\sqrt{-1}$ 。当n=0时,CPE 相当于一个电阻;n=1则相当于一个电容,n=0.5则相当于 Warburg 阻抗[23]。在本研究中, $Y_0$ 被当作一个假电容。

图 6.21 锡铜合金电极的 EIS 等效电路 1.

图 6.22 锡铜合金电极的 EIS 等效电路 2.

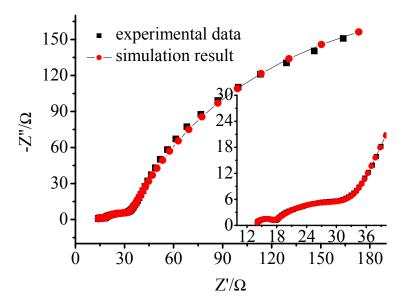

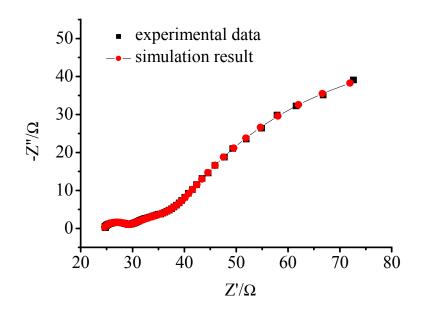

图 6.23 给出热处理后多孔铜上锡铜合金在 40℃下,首次嵌锂过程中,电位在 0.4 V时的实验数据和模拟结果。由曲线可知,模拟结果和实验数据能够很好地重合。再由其模拟参数值及其误差(表 6.1)可看出模拟得到的参数值误差较小,说明提出的模拟电路对实验数据进行模拟的合理性。

| 衣 6.1 热处 | 理归多孔铜上物铜合金在 40 0 条件下,目次散 |

|----------|--------------------------|

| 锂过程中,    | 电位在 0.4 V 时的的模拟参数值及其误差   |

|          |                          |

| Parameters                       | Simulation results | Error%  |

|----------------------------------|--------------------|---------|

| $R_s$                            | 13.78              | 0.58339 |

| R <sub>SEI</sub>                 | 3.342              | 4.5371  |

| Q <sub>SEI</sub> -Y <sub>0</sub> | 1.9206E-5          | 31.467  |

| Q <sub>SEI</sub> -n              | 0.84124            | 3.6407  |

| R <sub>ct</sub>                  | 17.52              | 1.6943  |

| Q <sub>dl</sub> -Y <sub>0</sub>  | 0.0039203          | 4.2701  |

| Q <sub>dl</sub> -n               | 0.59992            | 1.6279  |

| R <sub>P</sub>                   | 447.8              | 1.7075  |

| Q <sub>P</sub> -Y <sub>0</sub>   | 0.037327           | 0.66052 |

| Q <sub>P</sub> -n                | 0.83492            | 0.4295  |

### 6.4.4.3 不同温度下首次嵌锂过程 SEI 膜分析

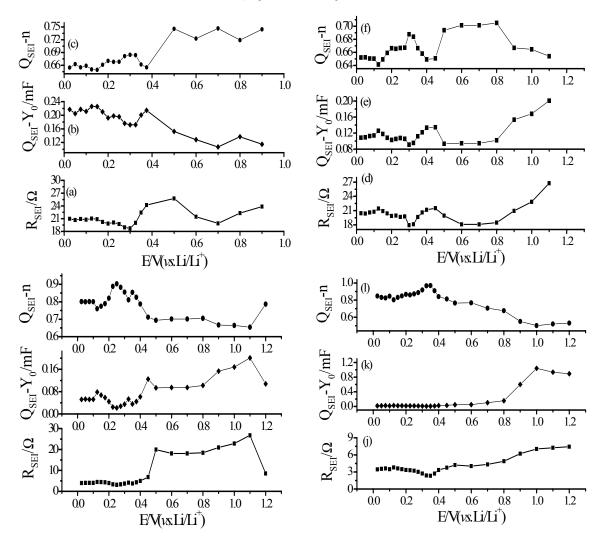

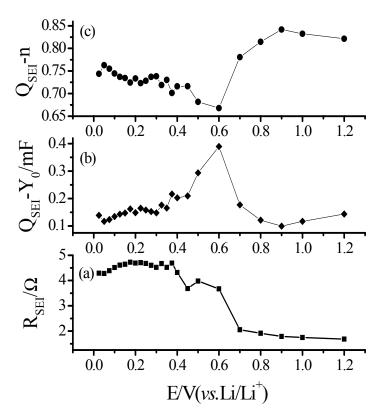

图 6.24 为热处理多孔铜上锡铜合金在 0  $^{\circ}$ C(a, b, c)、10  $^{\circ}$ C(d, e, f)、25  $^{\circ}$ C(g, h, i)和 40  $^{\circ}$ C(j, k, l)条件下,首次嵌锂过程中 R<sub>SEI</sub>、Q<sub>SEI</sub>-Y<sub>0</sub>和 Q<sub>SEI</sub>-n 随电极电位的变化图。由图可观察到不同温度条件下锡铜合金的 R<sub>SEI</sub>、Q<sub>SEI</sub>-Y<sub>0</sub>和 Q<sub>SEI</sub>-n 随电极电位的变化规律差别较大,且各自变化规律均较复杂。0  $^{\circ}$ C条件下,当电极电位大于 0.7 V 时,R<sub>SEI</sub> 随电极电位降低而减小;10  $^{\circ}$ C条件下也存在同样的现象;但 25  $^{\circ}$ C和 40  $^{\circ}$ C条件下 R<sub>SEI</sub> 随着电极电位的降低量较小,说明该两个温度下,高电位形成的 SEI 膜较稳定。同时我们可观察到 0  $^{\circ}$ C和 10  $^{\circ}$ C条件下,当电极电位分别在 0.7 V~0.5 V 和 0.7 V~0.45 V 范围内时, R<sub>SEI</sub> 随着电极电位的降低逐渐增大,指示 SEI 膜增厚,此现象在 25  $^{\circ}$ C和 40  $^{\circ}$ C下高电位下形成的 SEI 膜比较稳定。但当电极电位继续降低至 0.4 V 附近时,4 个温度下的 R<sub>SEI</sub> 值均减小,且在 0.3 V 附近达到极小值,指示 SEI 膜的破裂。由充放电结果可知,在 0.4V 附近时,Cu<sub>6</sub>Sn<sub>5</sub> 合金出现了一个明显的相变过程,此过程造成体积急剧膨胀, SEI 膜破裂,导致 R<sub>SEI</sub> 值减小。当电极电位进一步降低时,R<sub>SEI</sub> 随着电极电位的降低均增大,然后基本稳定,指示当电极电位低于 0.3 V 后,电解液在由于 SEI 膜破裂露出的新鲜电极表面上再次还原分解,生成 SEI 膜,R<sub>SEI</sub> 值再次增大,最后趋于稳定。

由  $Q_{SEI}$ - $Y_0$  对电极电位的变化曲线可观察到 4 个温度下的锡铜合金电极的  $Q_{SEI}$ - $Y_0$  随电极电位的变化规律与对应  $R_{SEI}$  随电极电位的变化规律相似。0  $\mathbb{C}$  条件下,当电极电位大于 0.4 V 时, $Q_{SEI}$ - $Y_0$  随电极电位的降低逐渐增大,与  $R_{SEI}$  的增大相对应,指示随电极电位的降低,高介电常数 SEI 膜成分(如烷基碳酸锂与痕量水反应生成  $Li_2CO_3$ )的生成;但当电极电位小于 0.4 V 后,与  $R_{SEI}$  相似,由于 SEI 膜的破裂导致  $Q_{SEI}$ - $Y_0$  减小。当电极电位小于 0.3 V 后  $Q_{SEI}$ - $Y_0$  随着电极电位的降低缓慢增大,然后基本稳定,指示SEI 膜趋于稳定。10  $\mathbb{C}$  和 25  $\mathbb{C}$  条件下锡铜合金电极的  $Q_{SEI}$ - $Y_0$  随电极电位的变化与 0  $\mathbb{C}$  条件下较为相似,同样经历了一个复杂的变化过程;但 40  $\mathbb{C}$  条件下锡铜合金电极的  $Q_{SEI}$ - $Y_0$  随电极电位的变化较为简单,随着电极电位降低整体趋势为减小。

由图 6.24 还可观察到 4 个温度下的锡铜合金电极的  $Q_{SEI}$ -n 随电极电位的变化规律均与相应  $Q_{SEI}$ -Y<sub>0</sub>和  $R_{SEI}$ 的变化规律基本相反。0  $^{\circ}$ C条件下,当电极电位大于 0.5 V 时,  $Q_{SEI}$ -n 随电极电位的变化较小。当电极电位在 0.5 V $^{\circ}$ 0.375 V 范围内, $Q_{SEI}$ -n 随电极电位的降低迅速减小,在 0.375 V 处出现极小值。这是由于在 0.375 V 附近,锂离子的嵌入

导致体积膨胀,SEI 膜的均匀度减小,所以  $Q_{SEI}$ -n 在 0.375 V 处出现极小值。但当电极电位降低到位于 0.375 V~ 0.325 V 范围内, $Q_{SEI}$ -n 随电极电位的降低而增大;当电极电位降低到 0.325 V 后, $Q_{SEI}$ -n 随电极电位降低开始缓慢减小,当电极电位降低至 0.15 V 后  $Q_{SEI}$ -n 基本稳定,指示 SEI 膜稳定。10  $\mathbb{C}$  条件下的情况与 0  $\mathbb{C}$  条件下的情况相似。25  $\mathbb{C}$  和 40  $\mathbb{C}$  时  $Q_{SEI}$ -n 随电极电位的变化规律与 0  $\mathbb{C}$  和 10  $\mathbb{C}$  时的变化规律略有不同。25  $\mathbb{C}$  时,当电极电位大于 0.25 V, $Q_{SEI}$ -n 随电极电位的降低先缓慢增大然后迅速增大,指示 SEI 膜均匀度增加;但当电极电位小于 0.25 V 后, $Q_{SEI}$ -n 随电极电位的降低先缓慢减小,然后达到基本稳定,指示 SEI 膜稳定,这与  $R_{SEI}$  和  $Q_{SEI}$  的分析结果一致。40  $\mathbb{C}$  时情况与 25  $\mathbb{C}$  时情况虽相似,但  $Q_{SEI}$ -n 达到极大值的电位为 0.35 V,且电极电位小于 0.35 V后基本稳定。比较不同温度下  $R_{SEI}$ ,  $Q_{SEI}$ -Y<sub>0</sub> 和  $Q_{SEI}$ -n 的值可知,随着温度的升高,

图 6.24 热处理多孔铜上锡铜合金在  $0^{\circ}$ C(a, b, c)、 $10^{\circ}$ C(d, e, f)、 $25^{\circ}$ C(g, h, i)和  $40^{\circ}$ C(j, k, l)下,首次嵌锂过程中  $R_{SEI}$ ,  $Q_{SEI}$ -Y<sub>0</sub>和  $Q_{SEI}$ -n 随电极电位的变化图

$R_{SEI}$ 和  $Q_{SEI}$ - $Y_0$ 均减小,而  $Q_{SEI}$ -n 却增大。由于温度升高锂离子的迁移速度增大,所以  $R_{SEI}$ 减小。 $Q_{SEI}$ - $Y_0$ 和  $Q_{SEI}$ -n 值随温度变化指示不同温度下生成 SEI 膜成分不同。以上 结果分析可知 40°C和 25°C下形成的 SEI 膜相对于 0°C和 10°C下更加均匀、稳定。

## 6.4.4.4 不同温度下首次脱锂过程 SEI 膜分析

图 6.25 热处理多孔铜上锡铜合金在  $0^{\circ}$ C(a, b, c)、 $10^{\circ}$ C(d, e ,f)、 $25^{\circ}$ C(g, h, i)和 40  $^{\circ}$ C(j, k, l)下,首次脱锂过程中  $R_{SEI}$ ,  $Q_{SEI}$ -Y<sub>0</sub>和  $Q_{SEI}$ -n 随电极电位的变化图

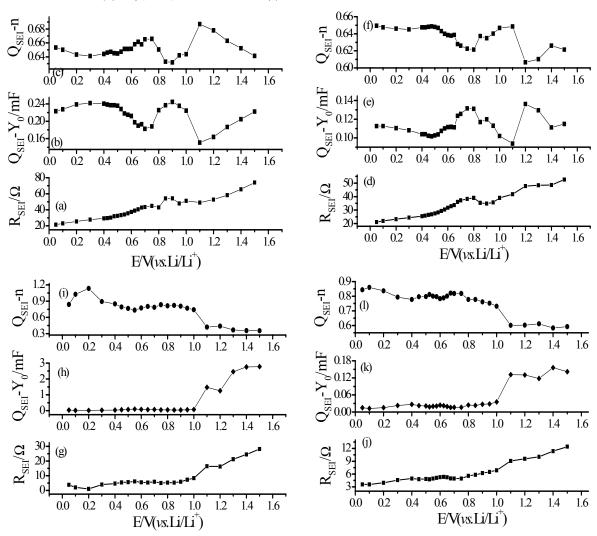

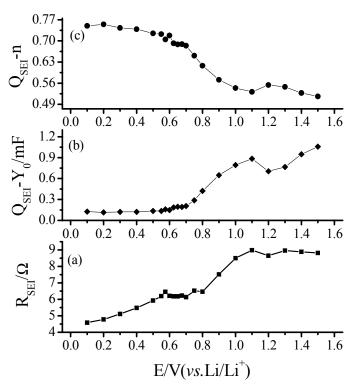

热处理后多孔铜上锡铜合金在 0℃(a, b, c)、10℃(d, e, f)、25℃(g, h, i)和 40℃(j, k, l)下,首次脱锂过程中  $R_{SEI}$ ,  $Q_{SEI}$ -Y<sub>0</sub>和  $Q_{SEI}$ -n 随电极电位的变化如图 6.25 所示。由图可观察到首次脱锂过程中不同温度下  $R_{SEI}$  随电极电位的变化规律比较简单,即随电极电位的增大先缓慢增大,后迅速增大,这是由于电解液在因体积收缩露出的新鲜电极表面再次

分解所致。比较不同温度下的  $R_{SEI}$  的变化规律可得出随电极电位升高 0  $\mathbb{C}$  和 10  $\mathbb{C}$  下  $R_{SEI}$  增加值较 40  $\mathbb{C}$  和 25  $\mathbb{C}$  下大。由图还可观察到不同温度下  $R_{SEI}$  均在 1.0  $\mathbb{V}$  附近急剧增大,说明电极充放电上限电位应小于 1.0  $\mathbb{V}$ 。

25℃和 40℃下的锡铜合金的  $Q_{SEI}$ - $Y_0$ 随电极电位的变化规律与对应  $R_{SEI}$ 基本一致,随着电极电位的增大先缓慢增大,然后迅速增大。0℃和 10℃条件下锡铜合金的  $Q_{SEI}$ - $Y_0$ 随电极电位的变化规律较为复杂。0℃条件下,当电极电位小于 0.45 V 时, $Q_{SEI}$ - $Y_0$ 随电极电位的增大变化较小,当电极电位大于 0.45 V 后  $Q_{SEI}$ - $Y_0$ 随电极电位的增大逐渐减小,可能是由于合金电极在脱锂过程中体积收缩所致。当电极电位增大到 0.7 V 后  $Q_{SEI}$ - $Y_0$ 随电极电位的增大又迅速增大,当电极电位增大到 0.9 V 后  $Q_{SEI}$ - $Y_0$ 0随电极电位的增大又迅速增大,这可能是由于不同电位下生成 SEI 膜成分不同所致。10℃时  $Q_{SEI}$ - $Y_0$ 0随电极电位的变化规律与 0℃时基本一致。

25℃和 40℃下的  $Q_{SEI}$ -n 随电极电位的变化规律与对应  $R_{SEI}$ 和  $Q_{SEI}$ -Y<sub>0</sub>恰好相反:随着电极电位的升高  $Q_{SEI}$ -n 先缓慢减小,1.0 V 附近迅速减小,然后基本稳定,指示脱锂过程中 SEI 膜均匀度缓慢减小,当电解液在电极表面还原后 SEI 膜均匀度迅速减小。0 ℃和 10℃下, $Q_{SEI}$ -n 随电极电位的变化规律与对应  $Q_{SEI}$ -Y<sub>0</sub>恰好相反,经历了一个复杂的变化过程。

#### 6.4.4.5 不同温度下首次嵌锂过程的电荷传递阻抗分析

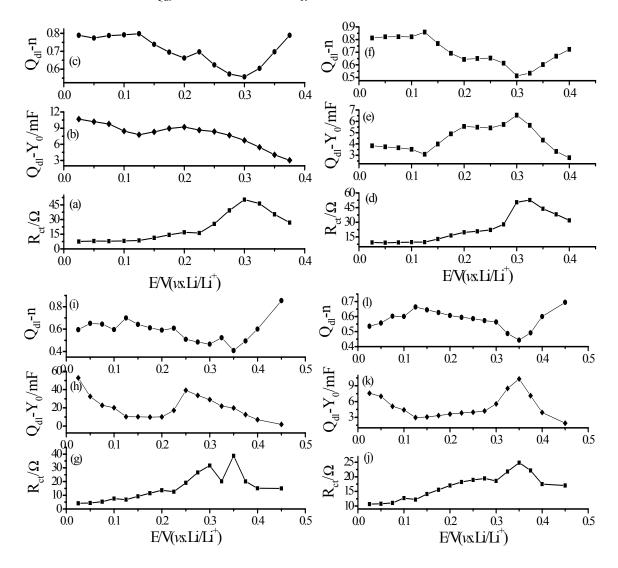

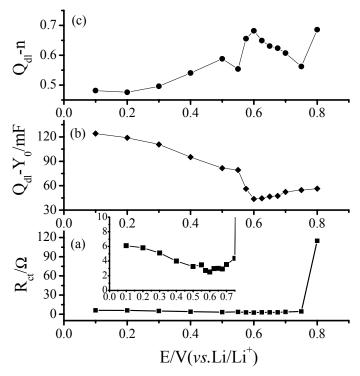

热处理后多孔铜上锡铜合金在 0℃(a, b, c)、10℃(d, e, f)、25℃(g, h, i)和 40℃(j, k, l) 条件下,首次嵌锂过程中  $R_{ct}$ ,  $Q_{dl}$ - $Y_0$ 和  $Q_{dl}$ -n 随电极电位的变化示于图 6.26。由图可观察到不同温度条件下  $R_{ct}$  随电极电位的变化规律较为相似,均经历了一个先增大后减小的过程,但转变电位略有不同。0℃时,当电极电位大于 0.3 V 时, $R_{ct}$  随电极电位的降低逐渐增大,当电极电位小于 0.3 V 后  $R_{ct}$  随电极电位的降低又逐渐减小。从充放电曲线可知  $Cu_6Sn_5$  合金在 0.4 V 附近出现了一个电位平台,根据文献报道在电位平台区  $R_{ct}$  应该出现极小值,与我们的实验结果相吻合。当电极电位进一步降低时,由于  $Cu_6Sn_5$  合金出现了新的嵌锂平台(0.1 V 附近),所以  $R_{ct}$  随电极电位降低逐渐减小,当电极电位降低到 0.125 V 后  $R_{ct}$ 基本稳定。庄全超等 $[^{24}]$ 研究石墨电极时也出现了此现象,但不明显,只是当电极电位低于石墨的主要放电平台 0.2 V 后  $R_{ct}$  略有增大,我们认为这是由于石墨

电极嵌锂电位区间较窄,难以分辨的缘故。10°C时,在电位为0.4 V~0.325 V 范围内, $R_{ct}$  随电极电位的减小逐渐增大,当电极电位小于0.3 V 后  $R_{ct}$  随电极电位的减小迅速减小,当电极电位降低到0.125 V 时  $R_{ct}$  基本稳定,其变化规律与0°C时的情况相似。25 °C 时,当电极电位位于0.45 V~0.35 V 范围内时, $R_{ct}$  随电极电位降低逐渐增大,0.35 V 时出现极大值,当电极电位小于0.35 V 后  $R_{ct}$  随电极电位降低先迅速减小,然后缓慢减小,最后基本稳定。40 °C 时,当电极电位位于0.5 V~0.375 V 范围内时, $R_{ct}$  随电极电位的减小先逐渐增大,0.375 V 时出现极大值,当电极电位小于0.375 V 后  $R_{ct}$  随电极电位的减小先迅速减小,然后缓慢减小,最后基本稳定。以上分析表明温度对  $R_{ct}$  随电极电位的变化规律无明显影响,但出现极大值的电位略有差别。不同温度下  $Q_{dl}$ - $Y_0$  经历了一个与  $R_{ct}$ 相似的变化过程,而  $Q_{dl}$ - $R_{ct}$  经历了一个与  $R_{ct}$  相反的变化过程。

图 6.26 热处理多孔铜上锡铜合金在  $0^{\circ}$ C(a, b, c)、 $10^{\circ}$ C(d, e, f)、 $25^{\circ}$ C(g, h, i)和  $40^{\circ}$ C(j, k, l)下,首次嵌锂过程中  $R_{ct}$ ,  $Q_{dl}$ -Y<sub>0</sub>和  $Q_{dl}$ -n 随电极电位的变化图

## 6.4.4.6 不同温度下首次脱锂过程的电荷传递阻抗分析

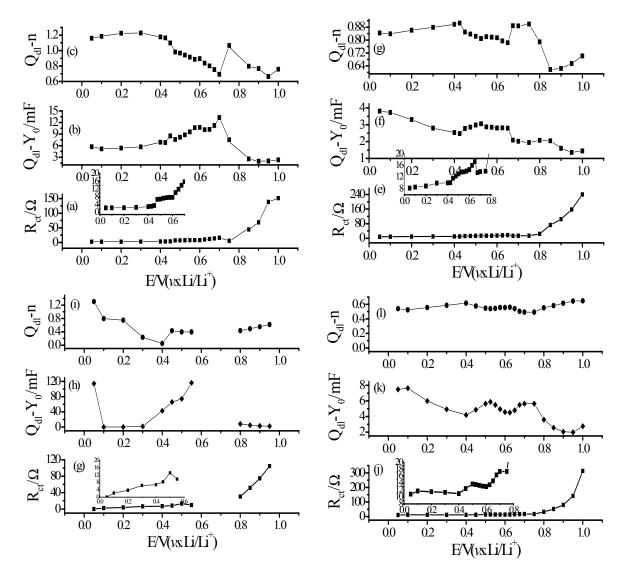

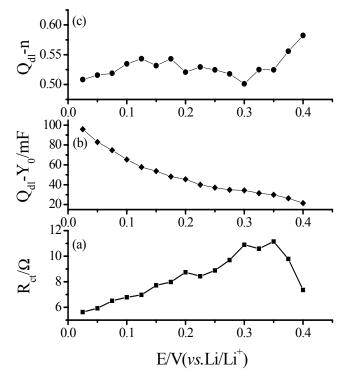

图 6.27 给出了热处理多孔铜上  $Cu_6Sn_5$  合金在  $0^{\circ}C(a,b,c)$ 、 $10^{\circ}C(d,e,f)$ 、 $25^{\circ}C(g,h,i)$  和  $40^{\circ}C(j,k,l)$ 条件下,首次脱锂过程中  $R_{ct}$ ,  $Q_{dl}$ - $Y_0$  和  $Q_{dl}$ -n 随电极电位的变化图。由图可观察到,不同温度下的  $R_{ct}$  随电极电位的升高先缓慢增大,当电极电位大于 0.8 V 后迅速增大。由于  $Cu_6Sn_5$  合金的脱锂过程主要主要发生在电极电位小于 0.8 V 范围内,当电极电位大于 0.8 V 后,大部分锂已经脱出,锂的脱出变得困难,所以  $R_{ct}$ 迅速增大。同时我们可观察到当电极电位大于 0.4 V 后,即锂离子开始脱出,不同温度下  $Q_{dl}$ - $Y_0$  随电极电位的变化规律与  $R_{ct}$  相似。但当  $R_{ct}$  迅速增大后,不同温度下  $Q_{dl}$ - $Y_0$  却均迅速减小,这可能是由于脱锂变得困难所致。 $0^{\circ}C$  和  $10^{\circ}C$  下的  $Q_{dl}$ -n 随电极电位的变化较复杂,

图 6.27 热处理多孔铜上  $Cu_6Sn_5$  合金在  $0^{\circ}C(a,b,c)$ 、 $10^{\circ}C(d,e,f)$ 、 $25^{\circ}C(g,h,i)$ 和  $40^{\circ}C(j,k,l)$ 条件下,首次脱锂过程中  $R_{ct}$ ,  $Q_{dl}$ - $Y_0$  和  $Q_{dl}$ -n 随电极电位的变化图

无明显规律; 25 ℃时, $Q_{dl}$ -n 随电极电位升高先缓慢减小,然后达到基本稳定; 40℃时, $Q_{dl}$ -n 随电极电位升高无明显变化,这可能与电极表面 SEI 膜稳定性有关。我们从前面的分析可知 25℃和 40℃下电极表面 SEI 膜较稳定。

### 6.4.4.7 不同温度下首次嵌锂过程的相变阻抗分析

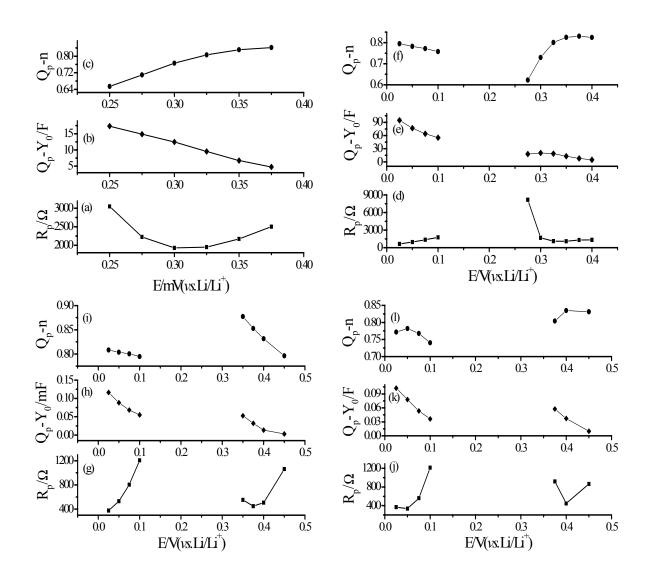

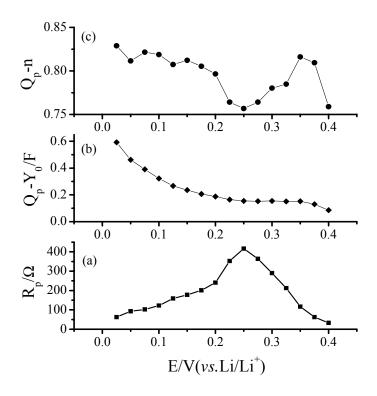

热处理后多孔铜上锡铜合金在 0℃(a, b, c)、10℃(d, e,f)、25℃(g, h, i)和 40℃(j, k, l) 条件下,首次嵌锂过程中  $R_p$ ,  $Q_p$ - $Y_0$ 和  $Q_p$ -n 随电极电位的变化由图 6.28 给出。0° $\mathbb{C}$ 时, 只有在 0.375 V~0.25 V 电位区间内出现了相变阻抗。由图可知 0℃时 Rp 随电极电位的减 小先迅速减小, 然后缓慢减小, 在 0.3 V 处出现极小值, 然后 R<sub>P</sub> 随电极电位的降低又迅 速增大,此过程  $Q_p$ - $Y_0$ 一直增大,  $Q_p$ -n减小,表明了锡铜合金在该电位范围内经历了相 变出现到消失的过程。10℃时,当电极电位在0.4 V~0.35 V 范围内  $R_P$  随电极电位的降 低缓慢减小, $Q_p-Y_0$ 缓慢增大, $Q_p-n$ 减小,表明此电位区间出现了明显的相变过程,当 电极电位小于 0.35 V 后 R<sub>P</sub> 随电极电位降低先缓慢增大, 到达 0.3 V 时迅速增大, 表明 相变过程的消失,这与充放电结果相一致。电位在 0.1 V~0.025 V 范围内 R<sub>P</sub> 随电极电 位的降低缓慢减小, $Q_p-Y_0$ 缓慢增大, $Q_p-n$  也缓慢增大,表明此电位区间再次出现明显 的新相变过程, 此现象同样与充放电结果相一致。25℃时, 当电极电位为 0.45 V~0.375 V 范围内时, $R_P$ 随电极电位的降低迅速减小,当电极电位小于  $0.375~V~fi~R_P$ 随电极电位 的降低迅速增大直到消失, $Q_p$ - $Y_0$ 迅速增大, $Q_p$ -n 也迅速增大。当电极电位为 0.1 V-0.025V 范围内  $R_p$  随电极电位的降低逐渐减小, $Q_p$ - $Y_0$  迅速增大, $Q_p$ -n 无明显变化。40℃时, 0.45  $V \sim 0.375 \, V$  电位区间内  $R_P$  随电极电位的降低先减小后迅速增大直到完全消失; 在该电位 区间内, $Q_p$ - $Y_0$ 迅速增大, $Q_p$ -n 无明显变化。当电极电位为 0.1~V-0.025~V 时, $R_P$  随电 极电位的降低先减小,到达0.05 V后略有增大;在该电位区间内, $Q_p$ - $Y_0$ 随电极电位降 低迅速增大, $Q_p$ -n 缓慢增大。我们知道  $Cu_6Sn_5$  合金在 0.4 V 和 0.1 V 附近均出现放电电 位平台,但不同温度下由于极化不同,所以出现电位平台的电位区间略有差别,相变阻 抗极小值出现电位略有不同。随着温度升高,极化减小,放电电位平台升高,所以相变 电阻出现极小值的电位升高。由图可观察到 0  $\mathbb{C}$  、10  $\mathbb{C}$  、25  $\mathbb{C}$  和 40  $\mathbb{C}$  条件下,0.4  $\mathbb{V}$  附 近相变阻抗极小值出现的电位分别在 0.3 V、0.35 V、0.375 V 和 0.4 V。由图还可以观察 到 0℃时 0.1 V 附近的相变阻抗未出现,这可能由于该温度下极化大导致锂离子在该电 位区间嵌入困难所致。40℃时,当电极电位为 0.1 V~0.025 V 时,R<sub>P</sub> 随电极电位的降低

先减小,到达  $0.05\,\mathrm{V}$  后略有增大,这是由于锂离子大量嵌入产生静电排斥所致。不同温度下  $\mathrm{Q_p-Y_0}$  随电极电位的降低均增大,这是由于生成新相的介电常数更大所致。

图 6.28 热处理后多孔铜上锡铜合金在  $0^{\circ}$ C(a, b, c)、 $10^{\circ}$ C(d, e,f)、 $25^{\circ}$ C(g, h, i) 和  $40^{\circ}$ C(j, k, l)下,首次嵌锂过程中  $R_p$ ,  $Q_p$ -Y<sub>0</sub>和  $Q_p$ -n 随电极电位的变化图

## 6.4.4.8 不同温度下首次脱锂过程的相变阻抗分析

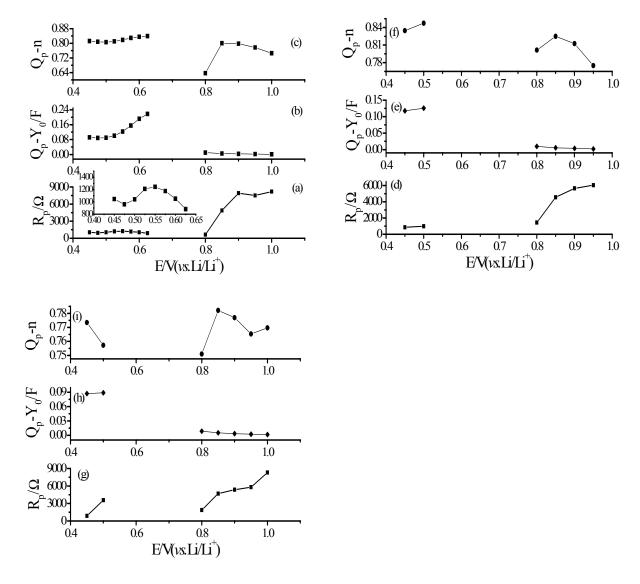

图 6.29 给出了热处理多孔铜上  $Cu_6Sn_5$  合金在  $10^{\circ}C(a,b,c)$ 、 $25^{\circ}C(d,e,f)$ 和  $40^{\circ}C(g,h,e)$ )下,首次脱锂过程中  $R_p$ ,  $Q_p$ - $Y_0$  和  $Q_p$ - $R_p$  随电极电位的变化图。 $10^{\circ}C$ 时, $0.45^{\circ}C$ 0.65 V电位范围内  $R_p$  随电极电位升高先减小,到达  $0.475^{\circ}C$ 1 后开始增大,这是由于  $0.475^{\circ}C$ 2 附近开始脱锂所致;该过程中  $Q_p$ - $Y_0$  和  $Q_p$ - $R_p$  均增大。当电极电位大于  $0.8^{\circ}C$ 2 化 极电位的升高迅速增大, $Q_p$ - $R_p$ 0 和  $R_p$ 0 和 R

40℃条件下,0.45 V 附近出现相变电位太少,所以无法看出其规律性;当电极电位大于 0.8 V 后  $R_p$ ,  $Q_p$ -Y<sub>0</sub>和  $Q_p$ -n 随电极电位的变化规律均与 10℃条件下一致。

图 6.29 热处理多孔铜上  $Cu_6Sn_5$  合金在  $10^{\circ}C(a, b, c)$ 、 $25^{\circ}C(d, e, f)$ 和  $40^{\circ}C(g, h, i)$ 下,首次脱锂过程中  $R_p, Q_p-Y_0$ 和  $Q_p$ -n 随电极电位的变化图

# 6.5 热处理后多孔铜上锡钴合金的性能研究

### 6.5.1 表面形貌和结构分析

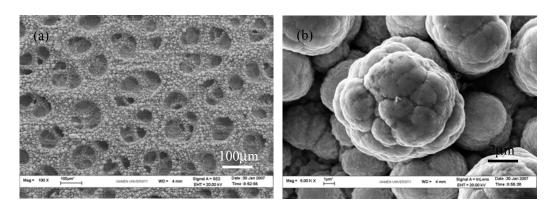

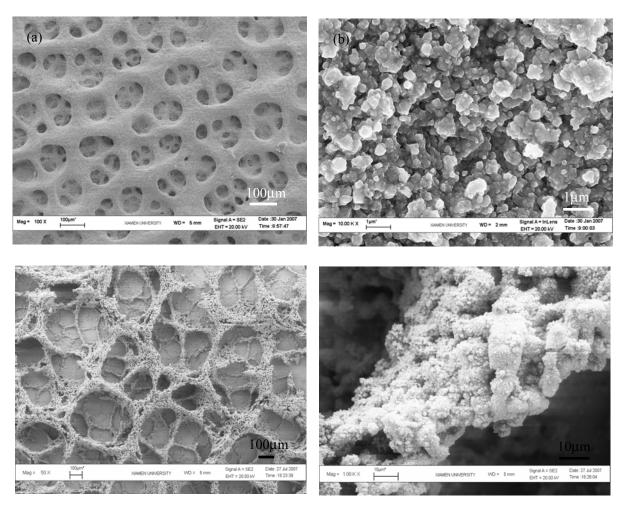

图 6.30 给出未经过热处理 (a, b) 和经过热处理后 (c, d) 多孔铜上锡钴合金的 SEM 图。由图 6.30 a 和图 6.30 b 可观察到锡钴合金沉积在多孔铜上保持了很好的多孔结构,但自身表现为无明显规则的形貌。图 6.30 c 和图 6.30 d 给出了热处理后多孔铜上电镀制

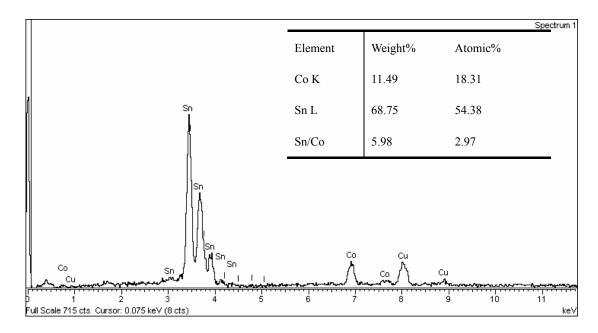

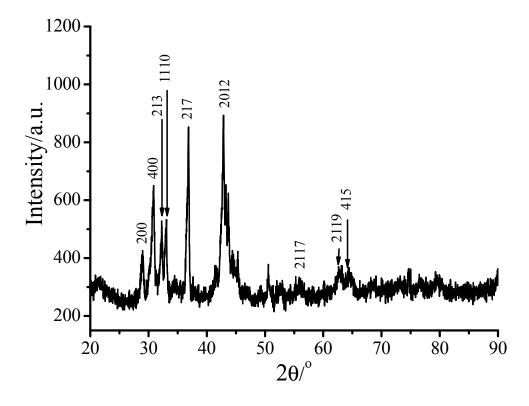

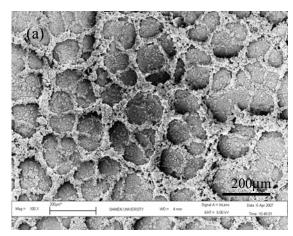

得锡钴合金的 SEM 图。由图可观察到锡钴合金无规则地沉积在多孔铜基底上,合金粒子之间存在一些不规则的缝隙,这些缝隙可以很好地缓解锡钴合金电极嵌锂过程产生的体积膨胀,达到改善锡钴合金电极充放电循环性能的目的。图 6.31 给出热处理后多孔铜上锡钴合金的 EDS 图。结果显示锡钴合金中锡钴成分的质量比和原子比分别为 5.98 和 2.97。再由热处理后多孔铜上锡钴合金的 XRD 图(如图 6.32)可观察到电镀得到的锡钴合金主要以四方晶型的 CoSn<sub>3</sub>组成,空间群为 I41/acd(JCPDS NO.00-048-1814),与 EDS 结果中锡钴成分原子比 2.97 基本一致。图 6.33 给出了热处理后多孔铜上锡钴合金经过 50 周充放电循环后的 SEM 图。由图可观察到锡钴合金仍然保持了很好的多孔性能。再由其局部放大图(图 6.33 b)可观察到由于体积膨胀导致孔壁上的缝隙消失,出现一些裂痕,但无明显的活性材料脱落,这是其改善锡钴合金电极充放电循环性能的一个重要原因。

图 6.30 未经过热处理(a, b) 和经热处理后(c, d) 多孔铜上锡钴合金的 SEM

图 6.31 热处理后多孔铜上锡钴合金的 EDS 图

图 6.32 热处理后多孔铜上锡钴合金的 XRD 图

图 6.33 热处理后多孔铜上锡钴合金充放电循环 50 周后的 SEM 图

### 6.5.2 热处理后多孔铜上锡钴合金的充放电循环性能

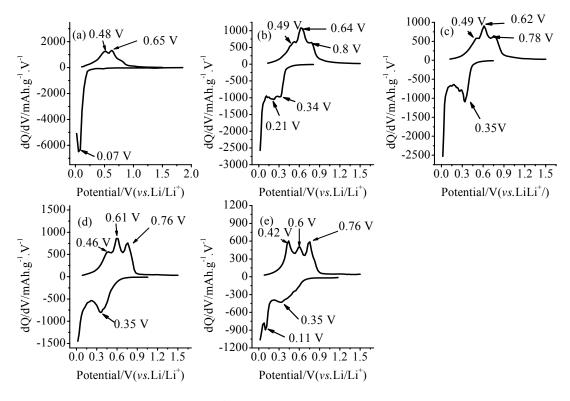

图 6.34 给出热处理后多孔铜上锡钴合金的充放电曲线(a)和循环性能曲线(b), 充放电电压范围为 0.02 V~1.5 V, 电流密度为 50 mA/g。热处理后多孔铜上锡钴合金充 放电 1 周(a)、2 周(b)、5 周(c)、20 周(d)和 50 周(e)循环的微分容量曲线由图 6.35 给出。 由图 6.34 a 和相应的微分容量曲线可观察到,锡钴合金首次放电(嵌锂)过程中在 0.07 V 附近给出一个电位平台, 首次充电(脱锂)过程中在 0.48 V 和 0.65 V 附近给出两个 电位平台。在第2周循环过程中锡钴合金在0.34 V和0.21 V附近出现了两个分离不明 显的放电电位平台;在第5周循环过程中转变为在0.35V附近给出一个放电电位平台; 且循环 20 周后仍然在 0.35 V 附近给出一个放电电位平台,但由相应微分容量曲线中峰 的尖锐度可知锡钴合金放电电位平台变得不明显。当锡钴合金电极充放电循环 50 周后, 锡钴合金在 0.35 V 和 0.11 V 附近给出两个放电电位平台,表明新相的生成[24,25]。由充 放电曲线和其相应的微分容量曲线可观察到,从第2周循环开始,锡钴合金电极的充电 曲线的平台电位无明显变化;但由微分容量曲线可观察到,当锡钴合金经过20周充放 电循环后, 在 0.46 V 和 0.76 V 附近的峰变得更加尖锐, 说明该两个电位平台变得更加 明显。图 6.34 b 给出锡钴合金的循环性能曲线。由曲线可得出锡钴合金首次放电容量为 726 mAh/g, 首次充电容量为 563 mAh/g, 首次库伦效率为 77.6%。由图还可看出第 2 周 循环容量相对于第周1循环容量衰减较大,这可能是由于合金电极体积膨胀导致部分活 性材料包埋在电极内部,无法参与锂离子的脱出。由图还可观察到,锡钴合金经过2周 循环后容量衰减变缓慢。

图 6.34 热处理后多孔铜上锡钴合金的充放电曲线 (a) 和循环性能曲线 (b),充放电电压范围为  $0.02\,\mathrm{V}\sim1.5\,\mathrm{V}$ ,电流密度为  $50\,\mathrm{mA/g}$

图 6.35 热处理后多孔铜上锡钴合金充放电 1 周(a)、2 周(b)、5 周(c)、20 周(d)和 50 周(e)循环的微分容量曲线

### 6.5.3 热处理后多孔铜上锡钴合金的 CV 研究

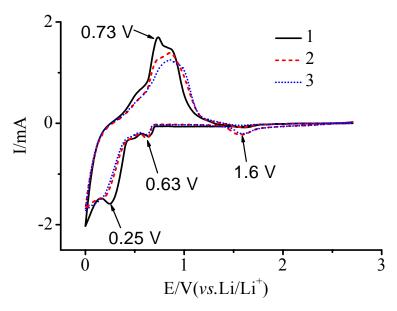

图 6.36 给出热处理后多孔铜上锡钴合金的 CV 图,扫描速度 v=0.1 mV/s。由图可观察到锡钴合金在首次嵌锂过程中,在 1.6 V 附近给出一个较小的还原峰,该峰在第 2 周

和第 3 周循环时开始增大,这是电解液分解以及水的还原所致。由于经过 1 周循环后锡钴合金电极体积膨胀,与电解液接触的表面积增大,所以第 2 周和第 3 周循环在此处的峰电流明显大于第 1 周循环。由图还可观察到在所有的循环中在 0.63 V 附近锡钴合金均出现了还原峰,这是纯锡的嵌锂峰。首次嵌锂过程中在 0.25 V 出现了一个大的嵌锂峰,此峰为锡钴合金的特征嵌锂峰,在随后的循环中此峰变得不明显。首次脱锂过程中,锡钴合金主要在 0.73 V 附近出现一个脱锂峰,此后的循环中变为一个宽峰,这与嵌锂峰相对应。

图 6.36 热处理后多孔铜上锡钴合金的 CV 图,扫描速度  $\nu$ =0.1 mV/s

### 6.5.4 热处理后多孔铜上锡钴合金的 EIS 研究

#### 6.5.4.1 热处理后多孔铜上锡钴合金的 EIS 的基本特征

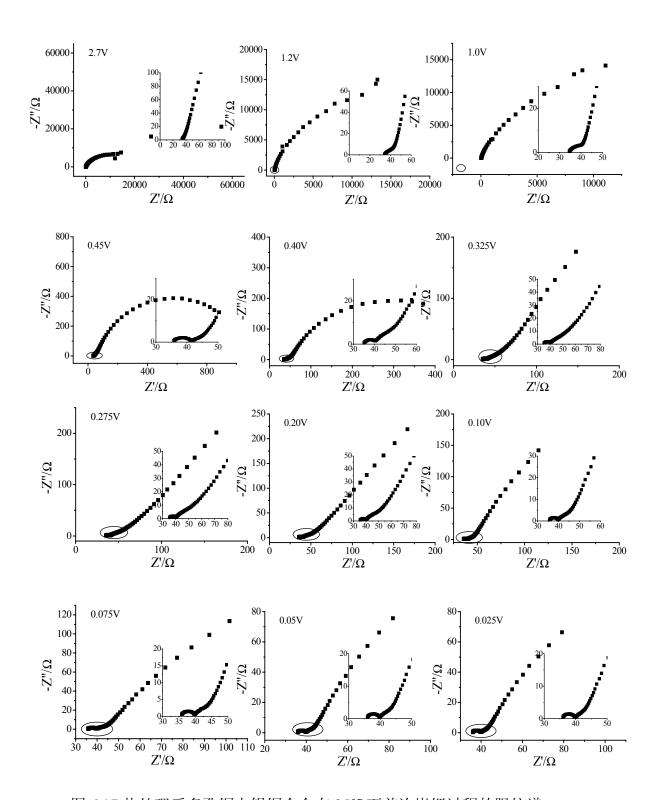

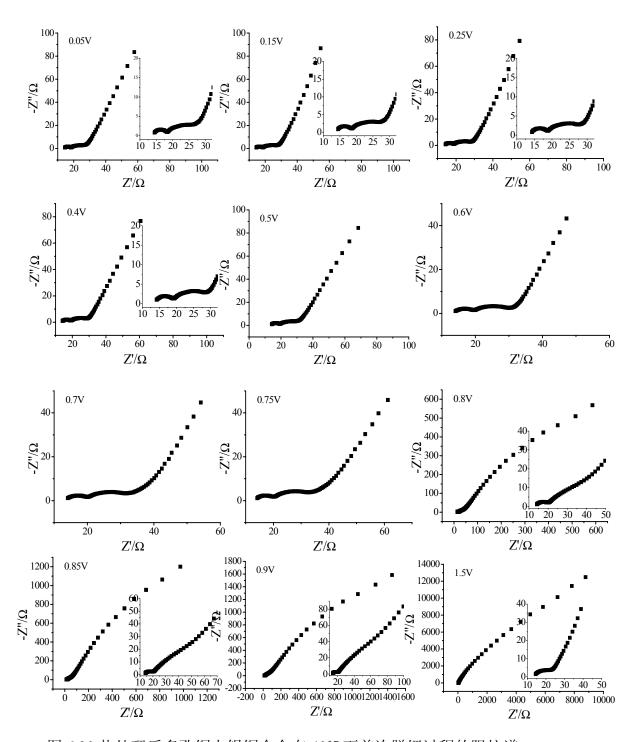

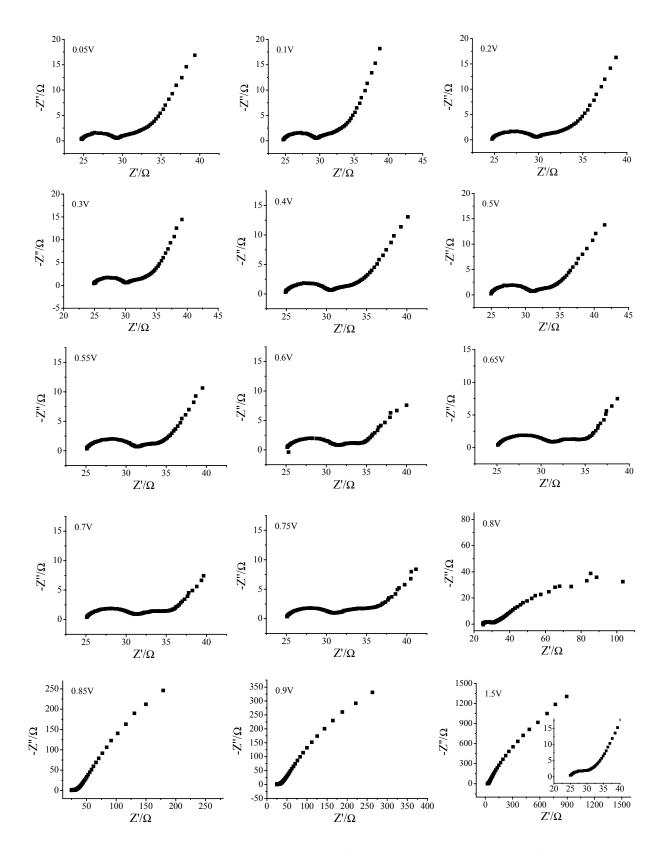

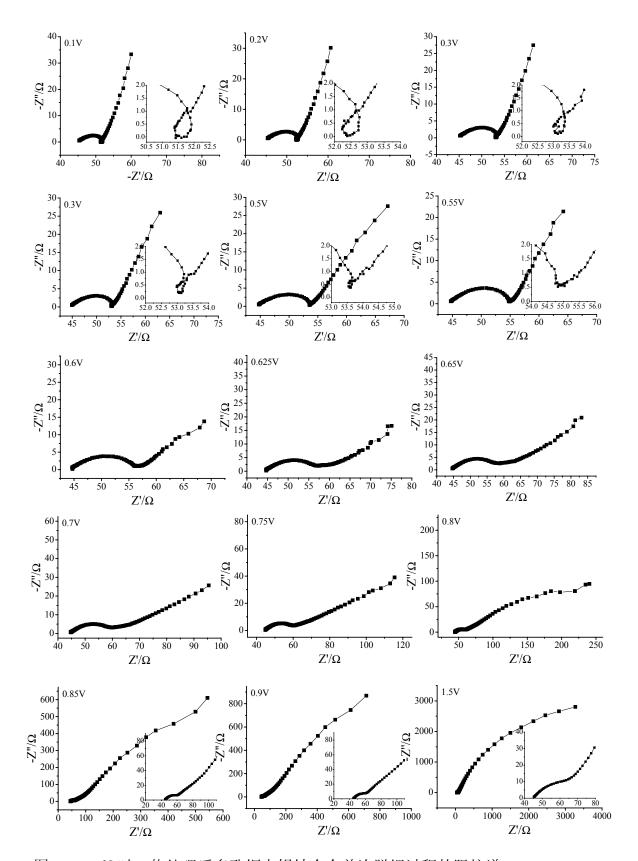

25℃下,热处理后多孔铜上锡钴合金首次嵌锂过程中在不同极化电位下的阻抗谱如图 6.37 所示。由图可看出,开路电位 2.7 V 时,Nyquist 图由高频一段分离不明显的圆弧和中低频曲率半径很大的圆弧组成。当电极电位降低至 1.2 V 时,高频由一段较小的圆弧和中低频一段很大的圆弧组成;当电极电位进一步降低到 0.6 V 后,低频圆弧曲率半径开始减小。当电极电位降低至 0.45 V 时,我们可以观察到 Nyquist 图明显由高频圆弧、中频圆弧和低频较大的圆弧组成。 根据第 5 章的分析,我们认为高频圆弧代表锂离子穿过电极表面 SEI 膜的阻抗,中频圆弧代表电荷传递阻抗,低频圆弧代表相变阻抗。

且当电极电位极化到 0.4 V 时,我们可观察到此 3 段圆弧分离更加明显。当电极电位进一步降低时,低频圆弧曲率半径增大,在 0.225 V 时几乎转变为一直线;但当电极电位小于 0.225 V 后,低频圆弧又开始变得明显,且曲率半径逐渐减小。

图 6.37 25℃下, 热处理后多孔铜上锡钴合金首次嵌锂过程的阻抗谱

图 6.38 25℃下, 热处理后多孔铜上锡钴合金首次脱锂过程的阻抗谱

图 6.38 给出 25℃时热处理后多孔铜上锡钴合金首次脱锂过程,在不同极化电位下的阻抗谱。由图可观察到,当电极电位小于 0.55 V 时,随着电极电位升高,锡钴合金的Nyquist 图形状无明显变化,均由高频代表 SEI 膜阻抗的圆弧、中频代表电荷传递阻抗的圆弧和低频代表体相扩散的斜线组成。当电极电位增大到 0.6 V 后,低频斜线转变为一段圆弧,指示相变过程的出现。当电极电位增大到 0.7 V 时此圆弧再次转变为一条斜线,代表相变过程的结束。当电极电位增大到 0.8 V 时 Nyquist 图由高频圆弧和中低频大的圆弧组成,表明电荷传递阻抗的增大。当电极电位升高至 0.85 V 后,中低频圆弧曲率半径进一步增大,指示脱锂过程变得困难。当电极电位进一步升高至 1.5 V 时,Nyquist 图由高频圆弧和中低频曲率半径很大的圆弧组成,指示脱锂完毕。

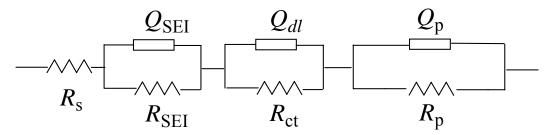

## 6.5.4.2 热处理后多孔铜上锡钴合金 EIS 的模拟电路选取

根据文献报道并结合实验结果我们提出了两种等效电路对实验数据进行模拟,如图 6.39和6.40。当阻抗谱为两段圆弧和一条斜线组成时运用等效电路1进行模拟,当阻抗谱 为3段圆弧组成时运用等效电路2进行模拟。其中 $R_s$ 代表欧姆电阻, $R_{SEI}$ 、 $R_{ct}$ 和 $R_p$ 分别为 SEI膜电阻、电荷传递电阻和晶体相变电阻,SEI膜电容 $C_{SEI}$ 、双电层电容 $C_{dl}$ 、晶体相变电容 $C_p$ 以及扩散阻抗分别用恒相角元件(CPE) $Q_{SEI}$ 、 $Q_{dl}$ 、 $Q_p$ 和 $Q_D$ 表示。CPE的导纳响应表达式如下:

$$Y = Y_0 \omega^n \cos\left(\frac{n\pi}{2}\right) + jY_0 \omega^n \sin\left(\frac{n\pi}{2}\right)$$

(6-2)

其中ω为角频率, j 为虚数单位 $\sqrt{-1}$ 。当n=0时,CPE 相当于一个电阻;n=1则相当于一个电容,n=0.5则相当于 Warburg 阻抗[23]。在本研究中, $Y_0$ 被当作一个假电容。

图 6.39 锡钴合金电极的 EIS 等效电路 1.

图 6.40 锡钴合金电极的 EIS 等效电路 2.

图 6.41 给出 25℃时热处理后多孔铜上锡钴合金首次嵌锂过程中,电位在 0.35 V 时的实验数据和模拟结果。由图可观察到模拟结果与实验所得阻抗谱具有很好的吻合性。 25℃时热处理后多孔铜上锡钴合金首次嵌锂过程中,在电位为 0.35 V 时的模拟参数值及 其误差列于表 6.2。由表 6.2 可得出模拟参数的误差较小。以上结果均表明采用我们提出的模拟电路能够很好地模拟我们的实验结果。

图 6.41 25℃时热处理后多孔铜上锡钴合金首次嵌锂过程中,电位为 0.35 V 时的实验数据和模拟结果

表 6.2 25℃时热处理后多孔铜上锡钴合金首次嵌锂过程中,电位为 0.35 V 时的模拟参数值及其误差

| Parameters                       | Simulation results | Error%  |

|----------------------------------|--------------------|---------|

| $R_s$                            | 24.47              | 0.10426 |

| R <sub>SEI</sub>                 | 4.523              | 1.7947  |

| Q <sub>SEI</sub> -Y <sub>0</sub> | 0.00016524         | 9.2466  |

| Q <sub>SEI</sub> -n              | 0.73036            | 1.3825  |

| R <sub>ct</sub>                  | 11.15              | 3.2252  |

| Q <sub>dl</sub> -Y <sub>0</sub>  | 0.029841           | 2.6991  |

| Q <sub>dl</sub> -n               | 0.52461            | 2.0526  |

| $R_{P}$                          | 116.5              | 1.6827  |

| Q <sub>P</sub> -Y <sub>0</sub>   | 0.15233            | 1.6576  |

| Q <sub>P</sub> -n                | 0.81614            | 0.65981 |

## 6.5.4.3 热处理后多孔铜上锡钴合金首次嵌/脱锂过程 SEI 膜分析

25℃时热处理后多孔铜上锡钴合金首次嵌锂过程中的  $R_{SEI}$ 、 $Q_{SEI}$ -Y<sub>0</sub>和  $Q_{SEI}$ -n 随电极电位的变化由图 6.42 给出。由图 6.42 a 可观察到随电极电位降低, $R_{SEI}$  先缓慢增大,当电极电位小于 0.7 V 后, $R_{SEI}$  迅速增大,指示 SEI 膜增厚。当电极电位降低到 0.375 V 后  $R_{SEI}$  基本稳定,但当电极电位小于 0.175 V 后  $R_{SEI}$  随电极电位的降低略有减小,表明 SEI 膜部分破裂。但我们从整个变化过程(特别是当电极电位小于 0.375 V 后)来看, $R_{SEI}$  变化的绝对值比较小,表明此条件下锡钴合金电极表面 SEI 膜比较稳定,有利于提高电池充放电循环性能。图 6.42 b 给出相应  $Q_{SEI}$ -Y<sub>0</sub> 随电极电位的变化。由图可观察到当电极电位大于 0.9 V 时, $Q_{SEI}$ -Y<sub>0</sub> 随电极电位的降低缓慢减小,指示 SEI 增厚。当电极电位小于 0.9 V 后, $Q_{SEI}$ -Y<sub>0</sub> 随电极电位的降低缓慢减小,指示 SEI 增厚。当电极电位小于 0.9 V 后, $Q_{SEI}$ -Y<sub>0</sub> 随电极电位的降低迅速增大,当电极电位为 0.6 V 时达到极大值,这可能是由于高介电常数 SEI 膜成分生成所致。但当电极电位进一步降低时, $Q_{SEI}$ -Y<sub>0</sub> 随电极电位的降低又迅速减小,当电极电位小于 0.35 V 后基本稳定,指示 SEI 膜稳定,

这与  $R_{SEI}$  结果相对应。图 6.42c 给出  $Q_{SEI}$ -n 随电极电位的变化图。由图可观察到  $Q_{SEI}$ -n 随电极电位的变化规律与  $Q_{SEI}$ -Y<sub>0</sub> 随电极电位的变化规律恰好相反。

图 6.42 25℃时热处理后多孔铜上锡钴合金首次嵌锂过程中 R<sub>SEI</sub>、Q<sub>SEI</sub>-Y<sub>0</sub>和 Q<sub>SEI</sub>-n 随电极电位的变化图

25℃时,热处理后多孔铜上锡钴合金首次脱锂过程中  $R_{SEI}$ 、 $Q_{SEI}$ - $Y_0$  和  $Q_{SEI}$ -n 随电极电位的变化示于图 6.43。由图可观察到当电极电位小于 0.55 V 时, $R_{SEI}$  随电极电位升高逐渐增大;当电极电位在 0.55 V~0.8 V 范围内  $R_{SEI}$  随电极电位的升高变化较小;当电极电位大于 0.8 V 后  $R_{SEI}$  随电极电位升高迅速增大;当电极电位大于 1.1 V 后  $R_{SEI}$  随电极电位的增大基本无变化,指示 SEI 膜达到稳定。图 6.43b 给出  $Q_{SEI}$ - $Y_0$  随电极电位的变化图。由图可以观察到电极电位小于 0.7 V 时  $Q_{SEI}$ - $Y_0$  随电极电位增大基本无变化,当电极电位大于 0.7 V 后开始迅速增大,大于 1.1 V 后基本稳定,与  $R_{SEI}$  结果一致,同样指示 SEI 膜达到稳定。 $Q_{SEI}$ -n 随电极电位的变化由图 6.43 c 给出。由图可观察到在整个电位区间内  $Q_{SEI}$ -n 随电极电位的升高先缓慢减小,后迅速减小,这是脱锂过程中体积收缩所致;当电极电位大于 1.1 V 后基本稳定,再次证明 SEI 膜达到稳定。

图 6.43 25℃时热处理后多孔铜上锡钴合金首次脱锂过程中 R<sub>SEI</sub>、Q<sub>SEI</sub>-Y<sub>0</sub>和 Q<sub>SEI</sub>-n 随电极电位的变化图

# 6.5.4.4 热处理多孔铜上锡钴合金首次嵌/脱锂过程中的电荷传递阻抗分析

图 6.44 25℃时热处理后多孔铜上锡钴合金首次嵌 锂过程中 R<sub>ct</sub>、Q<sub>dl</sub>-Y<sub>0</sub>和 Q<sub>dl</sub>-n 随电极电位的变化图

25℃时热处理后多孔铜上锡钴合金首次嵌锂过程中  $R_{ct}$ 、 $Q_{ct}$ - $Y_0$ 和  $Q_{ct}$ -n 随电极电位 的变化由图 6.44 所示。由图 6.44 a 可观察到,当电极电位为 0.4 V~0.35 V 范围内时,  $R_{ct}$  随电极电位的降低迅速增大;当电极电位大于 0.3 V 后又迅速减小。由锡钴合金的 CV 曲线可观察到其在 0.4 V 附近开始出现嵌锂,所以电荷传递阻抗较小,当电极电位 小于 0.3 V 后由于进入新的嵌锂区,所以电荷传递阻抗开始减小。图 6.44 b 给出  $Q_{dl}$ - $Y_0$  随电极电位的变化图。由图可观察到,在整个主要的放电区间(0.4 V~0.0 V), $Q_{dl}$ - $Y_0$  随着电极电位降低逐渐增大。在 0.4 V~0.0 V 电位区间内, $Q_{dl}$ -n 随电极电位降低无缓慢 减小,然后基本稳定,但整个过程的  $Q_{dl}$ -n 值均较小,指示均匀度较差。

图 6.45 25℃时热处理后多孔铜上锡钴合金首次脱锂过程中 R<sub>ct</sub>、Q<sub>dl</sub>-Y<sub>0</sub>和 Q<sub>dl</sub>-n 随电极电位的变化图

图 6.45 给出 25℃时热处理后多孔铜上锡钴合金首次脱锂过程中  $R_{ct}$ 、 $Q_{dl}$ - $Y_0$ 和  $Q_{dl}$ -n随电极电位的变化图。由图 6.45 a 可观察到,当电极电位小于 0.6 V 时, $R_{ct}$ 随电极电位的变化图。由图 6.45 a 可观察到,当电极电位小于 0.6 V 时, $R_{ct}$  随电极电位的升高逐渐减小,当电极电位在 0.6 V~0.75 V 范围内时, $R_{ct}$  基本无变化,指示该电位区间锂离子的大量脱出。当电极电位大于 0.75 V 后, $R_{ct}$  随电极电位的升高迅速增大,表明锂离子脱出开始变得困难,这与充放电结果相对应,充放电结果显示锂离子的脱出主要发生在电位 0.6 V 附近。图 6.45 b 给出  $Q_{ct}$ - $Y_0$  随电极电位的变化图。由图可观察到  $Q_{ct}$ - $Y_0$  随电极电位的升高先缓慢减小,当电极电位大于 0.55 V 后迅速减小,最后趋于基本稳定,

指示锂离子脱出完成,这与  $R_{ct}$ 得出结果一致。由图  $6.45\,c$  可以看出  $Q_{ct}$ -n 随电极电位的升高先缓慢增大,然后迅速增大, $0.6\,V$  时达到极大值。当电极电位进一步增大时, $Q_{ct}$ -n 随电极电位的增大又开始减小,这是锂离子脱出导致合金均匀度降低所致。

### 6.5.4.5 热处理多孔铜上锡钴合金相变阻抗分析

25°C时热处理后多孔铜上锡钴合金首次嵌锂过程中  $R_p$ 、 $Q_p$ -Y<sub>0</sub>和  $Q_p$ -n 随电极电位的变化示于图 6.46。可观察到  $R_p$ 、 $Q_p$ -Y<sub>0</sub>和  $Q_p$ -n 随电极电位的变化规律与首次嵌锂过程中  $R_{ct}$ 、 $Q_{dl}$ -Y<sub>0</sub>和  $Q_{dl}$ -n 随电极电位的变化规律相似。当电极电位在 0.4 V~0.25 V 电位范围 内时, $R_p$  随电极电位的降低逐渐增大,指示相变阻抗增大;当电极电位小于 0.25 V 后, $R_p$  随电极电位的降低又逐渐减小。与前面分析相似,由于在 0.4 V 附近锡钴合金开始嵌锂,所以相变电阻较小,当电位超出该相变区,相变电阻又增大,当电极电位小于 0.25 V 后,由于新相变的出现,所以相变电阻再次减小,直到嵌锂完毕。

图  $6.46\ 25$ °C时热处理后多孔铜上锡钴合金首次脱锂过程中  $R_p$ 、 $Q_p$ - $Y_0$  和  $Q_p$ -n 随电极电位的变化图

由图 6.46 b 所示的  $Q_p$ - $Y_0$  随电极电位的变化图可观察到  $Q_p$ - $Y_0$  随电极电位的降低先缓慢增大,然后迅速增大,这可能是由于体积膨胀导致表面积增大所致。图 6.46 c 给出

$Q_p$ -n 随电极电位的变化图。由图可以观察到  $Q_p$ -n 随电极电位的变化与  $R_p$  随电极电位的变化规律基本相反。

### 6.5.5 热处理多孔铜上锡钴合金感抗特性研究

众所周知,电化学阻抗谱中感抗特征经常出现在电催化、电沉积和电溶解过程中,但不同的体系产生感抗的机理不同<sup>[27-35]</sup>。目前主要分为下面三个:一是两相间(如氧化物和还原态)的电子和离子浓差产生的感抗;二是两个半导体间由于电子或空隙占据不同产生的感抗;三是两相接触时,电荷在其中一相中的驰豫产生感抗。庄全超等对LiCoO<sub>2</sub><sup>[38]</sup>和 LiMn<sub>2</sub>O<sub>4</sub><sup>[39]</sup>的研究表明当电极材料嵌/脱锂存在不均匀性时,产生局部的锂离子浓差电池,从而产生感抗。以上分析表明如果电极短路时,由于瞬时电流很大,造成电极表面嵌脱锂不均匀,所以易产生感抗行为。为了研究这一行为,我们人为将浸入电解液内的锡钴合金电极与锂片接触然后迅速分开,测试其首次嵌脱锂过程的阻抗行为。由于接触时间短,嵌/脱锂只发生在表面,所以电极分离后电位会回升至 2.0 V 以上。同时由于接触时间很短,在电极表面不能形成覆盖性良好的 SEI 膜。

### 6.5.5.1 热处理多孔铜上锡钴合金阻抗基本特征

图 6.47 给出 10℃时热处理后多孔铜上锡钴合金首次嵌锂过程中不同极化电位下的阻抗谱。由图可观察到在开路电位 2.3 V 时,Nyquist 图由一段曲率半径很大的圆弧组成,指示电极短路时未形成覆盖性良好的 SEI 膜。当电极电位极化到 1.3 V 后高频开始出现一段圆弧,代表 SEI 膜的生成。当电极电位进一步降低,高频圆弧分离更加明显,同时中低频圆弧曲率半径减小。当电极电位降低到 0.4 V 时,Nyquist 图主要由高频圆弧和中低频圆弧组成,同时在高频圆弧和低频圆弧连接处出现了乱点,这主要是由于电极表面不均匀性所致。当电极电位进一步降低到 0.375 V 时中低频圆弧曲率半径增大。当电极电位极化到 0.35 V 时,Nyquist 图分为 3 段圆弧:高频代表 SEI 膜阻抗的圆弧,中频代表电荷传递阻抗的圆弧和低频代表相变阻抗的圆弧,其中中频圆弧和低频圆弧分离不明显。当电极电位降低到 0.225 V 时,高频圆弧和中频圆弧之间出现了一小段感抗弧。当电极电位进一步降低,此感抗弧逐渐增大,然后基本恒定,指示在该电位区间随着锂离子的大量嵌入,合金电极均匀性降低。图 6.48 给出 10℃时热处理后多孔铜上锡钴合金首次脱锂过程中不同极化电位下的阻抗谱。由图可观察到当电极电位低于 0.6 V 时,

## Nyquist 图均由高频圆弧,中频感抗狐和电荷传递阻

图 6.47 10℃时, 热处理后多孔铜上锡钴合金首次嵌锂过程的阻抗谱。

图 5.48 10℃时, 热处理后多孔铜上锡钴合金首次脱锂过程的阻抗谱。

抗弧,以及低频斜线组成,其中感抗弧随着电极电位的增大逐渐减小。当电极电位升高到 0.6 V 时,感抗弧完全消失,Nyquist 图仅由高频圆弧、中频扁平圆弧和低频圆弧组成。当电极电位升高到 0.625 V 后,低频圆弧转变为斜线。当电极电位大于 0.75 V 后,由于锂离子大量脱出致使电荷传递阻抗增大,所以 Nyquist 图由高频圆弧和中低频曲率半径很大的圆弧组成,当电极电位进一步升高到 1.5 V 时该特征无明显变化。

### 6.5.5.2 等效电路的选取

根据文献报道和结合我们的实验结果我们提出了如图6.49的等效电路对实验数据进行模拟。视阻抗谱中相变阻抗弧和感抗弧出现与否来添加和去除 $R_PQ_P$ 和 $R_L$ L电路。其中 $R_S$ 代表欧姆电阻, $R_{SEI}$ 、 $R_L$ 、 $R_{ct}$ 和 $R_p$ 分别为SEI膜电阻、感抗电阻、电荷传递电阻和晶体相变电阻,SEI膜电容 $C_{SEI}$ 、双电层电容 $C_{dl}$ 、晶体相变电容 $C_p$ 以及扩散阻抗分别用恒相角元件(CPE) $Q_{SEI}$ 、 $Q_{dl}$ 、 $Q_p$ 和 $Q_D$ 表示,其中感抗由L表示。CPE的导纳响应表达式如下:

$$Y = Y_0 \omega^n \cos\left(\frac{n\pi}{2}\right) + jY_0 \omega^n \sin\left(\frac{n\pi}{2}\right)$$

(6-3)

其中 $\omega$ 为角频率, j 为虚数单位 $\sqrt{-1}$ 。当n=0时,CPE 相当于一个电阻;n=1则相当于一个电容,n=0.5则相当于 Warburg 阻抗[23]。在本研究中, $Y_0$ 被当作一个假电容。

图 6.49 锡钴合金的 EIS 等效电路